## UNIVERSIDADE ESTADUAL PAULISTA

## Instituto de Geociências e Ciências Exatas Campus de Rio Claro

# IMPLEMENTAÇÃO DE DUAS ARQUITETURAS MICROCONTROLADAS TOLERANTES A FALHAS PARA CONTROLE DA TEMPERATURA

Gilson Fernando Botta

Orientadora: Profa. Dra. Deisy Piedade Munhoz Lopes

Dissertação de Mestrado elaborada junto ao Programa de Pós-Graduação em Física – Área de Concentração em Física Aplicada, para obtenção do Título de Mestre em Física.

Rio Claro (SP) 2002 004.22 Botta, Gilson Fernando

B751i Implementação de duas arquiteturas

microcontroladas tolerantes a falhas para controle da temperatura / Gilson

Fernando Botta. – Rio Claro: [s.n.], 2002

113 f. : il., gráfs., tabs., fots.

Dissertação (Mestrado) - Universidade Estadual

Paulista,

Instituto de Geociências e Ciências exatas Orientador: Deisy Piedade Munhoz Lopes

1. Arquitetura de computador. 2. Tolerância a falha

(Computação). 3. Microcontroladores. 4.

Arquitetura TMR. 5. Arquitetura em anel. 6.

Sistema embarcado. I. Título.

Ficha catalográfica elaborada pela STATI – Biblioteca da UNESP Campus de Rio Claro/SP

## Comissão Examinadora

## Profa. Dra. Deisy Piedade Munhoz Lopes Instituição: IGCE/RC

Prof. Dr. Gerson Antonio Santarine Instituição: IGCE/RC

Prof. Dr. Ronaldo Guimaraes Correa Instituição: UFSCAR

Gilson Fernando Botta Aluno

Rio Claro, 17 de Dezembro de 2002

Resultado: Aprovado – com "Distinção e Louvor"

Dedico este trabalho a minha esposa Karina, aos meus pais, Edilberto e Arlete, aos meus avós, Pedro e Irene, Cirvo (in memoriam) e Albina, e a todos os parentes e amigos que compreenderam minha ausência.

## **Agradecimentos**

A Profa. Dra. Deisy Piedade Munhoz Lopes, pela orientação, amizade e incentivo, que foram fundamentais para realização deste trabalho.

Ao Prof. Dr. Gerson Antonio Santarine, pelo auxílio, apoio, amizade e pelas fotografias contidas no trabalho.

Ao Prof. Dr. Ronaldo Guimaraes Correa, pelas valiosas sugestões referentes ao trabalho.

A minha esposa Karina de Cássia Borges Botta, pelo incentivo e compreensão, durante todo o processo de desenvolvimento deste trabalho.

Aos Professores do Curso de Pós-Graduação em Física – Área de Concentração: Física Aplicada – da UNESP de Rio Claro, pelos ensinamentos transmitidos.

Ao Instituto de Geociências e ao Departamento de Física da UNESP de Rio Claro, pelo apoio e facilidades concedidos.

Ao José Roberto Locatelli Fonseca, Valter Rodrigues de Moraes, Danilo Carlos Pereira e Rodrigo Luiz Botta, pela cooperação, amizade e companheirismo.

Aos parentes e amigos que, direta ou indiretamente, me apoiaram no desenvolvimento deste trabalho.

"Também, assim como quereis que os homens façam a vós, fazei do mesmo modo a eles". Lucas 6:31

# **SUMÁRIO**

| Índice                                         | i    |

|------------------------------------------------|------|

| Resumo                                         | iv   |

| Abstract                                       | v    |

| Lista de Figuras                               | vi   |

| Lista de Fotografias                           | vii  |

| Lista de Tabelas                               | viii |

| Nomenclatura                                   | X    |

| Abreviações                                    | X    |

| Siglas                                         | X    |

| Capítulo 1 – Introdução                        | 01   |

| Capítulo 2 – Revisão da Literatura             | 05   |

| Capítulo 3 – Parte Experimental                | 22   |

| Capítulo 4 – Resultados e Discussões           | 44   |

| Capítulo 5 – Conclusões e Perspectivas Futuras | 52   |

| Referências Bibliográficas                     | 55   |

| Anexo I: MCU PIC 16F628                        | 63   |

| Anexo II: Arquivo Include para o PIC 16F628    | 108  |

## ÍNDICE

| 1 | INTRODU   | ÇÃO           |                                                        |

|---|-----------|---------------|--------------------------------------------------------|

| 2 | REVISÃO   | DA LI         | TERATURA                                               |

|   | 2.1 SISTE |               | MAS COMPUTACIONAIS TOLERANTES A FALHAS                 |

|   |           | 2.1.1         | Introdução                                             |

|   |           | 2.1.1         | Conceitos de erro, falha e defeito                     |

|   |           | 2.1.2         | Confiabilidade e disponibilidade                       |

|   |           | 2.1.3         | Utilização de recursos redundantes                     |

|   |           | 2.1.4         | Emprego de sistemas computacionais tolerantes a falhas |

|   | 2.2       | MICR          | OCONTROLADORES                                         |

|   |           | 2.2.1         | Definição                                              |

|   |           | 2.2.1         | Memória de dados                                       |

|   |           | 2.2.3         | Memória de Programa                                    |

|   |           | 2.2.4         | Processador                                            |

|   |           | 2.2.5         | Recursos Auxiliares                                    |

|   |           | 2.2.6         | Arquitetura                                            |

|   |           | 2.2.7         | Seleção de um Microcontrolador                         |

| 3 | PARTE EX  | <b>XPERIN</b> | MENTAL                                                 |

|   | 3.1       | MODI          | ELAGEM TEÓRICA                                         |

|   |           | 3.1.1         | Introdução                                             |

|   |           | 3.1.2         | Arquiteturas em anel e TMR                             |

|   | 3.2       | ANÁI          | JSE EXPERIMENTAL                                       |

|   |           | 3.2.1         | Hardware dos sistemas                                  |

|   |           | 3.2.2         | Software dos sistemas                                  |

|   |           | 3.2.3         | Estrutura do software da arquitetura em anel           |

|   |           | 3.3.3         | Estrutura do software da arquitetura TMR               |

|   |           | 3.3.4         | Considerações sobre os sistemas                        |

|   |           | 3.3.5         | A diferença entre o software das arquiteturas          |

|   |           |               | implementadas                                          |

|   |           | 3.3.6         | Peculiaridades do software de cada módulo              |

|   |           | 3.3.7         | Gravação do Microcontrolador                           |

| 4 | RESULTA   | DOS E DISCUSSÕES4                                        |

|---|-----------|----------------------------------------------------------|

|   | 4.1       | Considerações iniciais                                   |

|   | 4.2       | Utilização do módulo comparador na gestão da temperatura |

|   | 4.3       | Análise4                                                 |

| 5 | CONCLUS   | SÕES E PERSPECTIVAS FUTURAS 52                           |

|   | REFERÊN   | CIAS BIBLIOGRÁFICAS 55                                   |

|   | ANEXO I:  | MCU PIC 16F628                                           |

|   | MCU PIC 1 | 6F628                                                    |

|   | 1         | Principais características                               |

|   | 2         | Memória de programa                                      |

|   | 3         | Registradores                                            |

|   | 4         | Registradores de controle da CPU                         |

|   |           | 4.1 Registrador STATUS                                   |

|   |           | 4.2 Registrador OPTION                                   |

|   |           | 4.3 Registrador PCON                                     |

|   | 5         | Portas de entrada e saída                                |

|   |           | 5.1 Registradores TRISA E TRISB                          |

|   |           | 5.2 Registradores PORTA e PORTB                          |

|   | 6         | Interrupções                                             |

|   |           | 6.1 Registrador INTCON                                   |

|   |           | 6.2 Registrador PIE1                                     |

|   |           | 6.3 Registrador PIR1                                     |

|   | 7         | Contador de programa – PC                                |

|   | 8         | Contador/Temporizador TMR0                               |

|   | 9         | Contador/Temporizador Timer 1                            |

|   |           | 9.1 Registrador T1CON 82                                 |

|   | 10        | Módulo Timer 2                                           |

|   |           | 10.1 Registrador TMR2CON 8-                              |

|   | 11        | Módulo comparador                                        |

|   |           | 11.1 Registrador CMCON 8                                 |

|   | 12        | Módulo de referência interna de tensão                   |

|   | 13        | Módulo de Captura/Comparação/PWM                         |

|   |           | 13.1 Registrador CCP1CON 9                               |

|       | 1     | 3.2     | Registrador CCPR1L                               | 92  |

|-------|-------|---------|--------------------------------------------------|-----|

|       | 1     | 3.3     | Registrador CCPR1H                               | 92  |

|       | 1     | 3.4     | Modo de captura                                  | 93  |

|       | 1     | 3.5     | Modo de comparação                               | 93  |

|       | 1     | 3.6     | Modo PWM                                         | 94  |

| 14    | 4 I   | nterfa  | ce de comunicação serial                         | 95  |

|       | 1     | 4.1     | Transmissão/Recepção de dados no modo assíncrono | 96  |

|       | 1     | 4.2     | Transmissão/Recepção de dados no modo síncrono   | 96  |

|       | 1     | 4.3     | Registrador TXSTA                                | 97  |

|       | 1     | 4.4     | Registrador RCSTA                                | 98  |

|       | 1     | 4.5     | Registrador SPBRG                                | 99  |

| 15    | 5 N   | Memói   | ria EEPROM interna                               | 100 |

|       | 1     | 5.1     | Registrador EEADR                                | 100 |

|       | 1     | 5.2     | Registrador EEDATA                               | 101 |

|       | 1     | 5.3     | Registrador EECON1                               | 101 |

|       | 1     | 5.4     | Registrador EECON2                               | 102 |

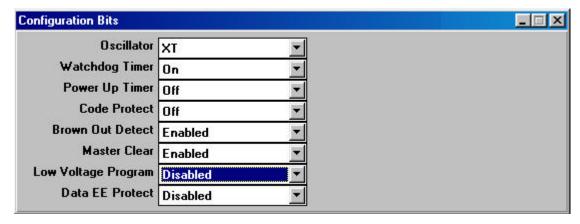

| 16    | 6 F   | Palavra | a de configuração                                | 102 |

| 17    | 7 (   | Config  | guração do oscilador do PIC 16F628               | 104 |

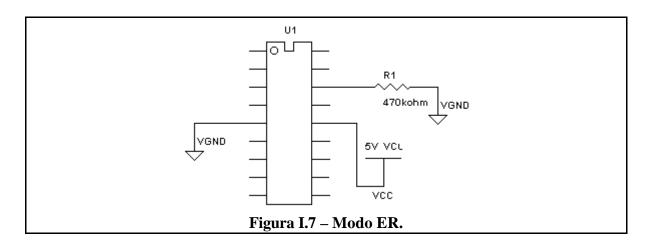

|       | 1     | 7.1     | Modo ER                                          | 105 |

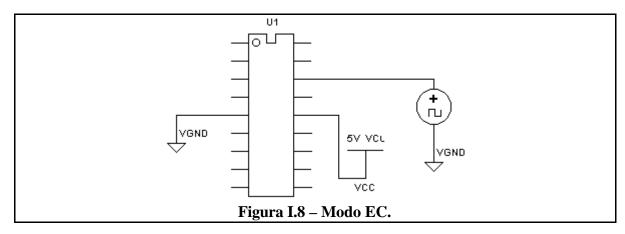

|       | 1     | 7.2     | Modo EC                                          | 105 |

|       | 1     | 7.3     | Modo INTRC                                       | 105 |

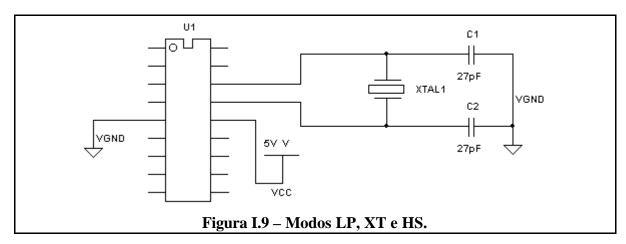

|       | 1     | 7.4     | Modos LP, XT e HS                                | 105 |

| ANEXO | II: A | AROU    | IVO INCLUDE PARA O PIC 16F628                    | 108 |

## Resumo

Os microcontroladores são empregados com frequência crescente na automação e controle de processos. É fato, que em certos processos, a falha no sistema de controle é inadmissível. Nestes casos, é necessário o emprego de técnicas de tolerância à falhas. Diante disso, duas arquiteturas com base em microcontroladores, foram projetadas, construídas e submetidas a testes. Tanto a Arquitetura em Anel como a Arquitetura TMR implementadas, podem suportar falhas tanto nos nodos da estrutura, como nos arcos, que representam as ligações entre microcontroladores. Os nodos são controlados por protocolos implementados por programação, sem a necessidade de um circuito votante comum, presente na arquitetura TMR clássica, ou de qualquer outro circuito especial, para o controle da redundância dos circuitos. Os sistemas são modulares e podem operar sem um dos módulos ativado. Isso permite que um determinado módulo seja retirado para manutenção e posteriormente reinstalado, de maneira transparente a aplicação. Foram realizados testes nas arquiteturas desenvolvidas, com injeção de falhas físicas e lógicas. Ambas as arquiteturas responderam conforme o desejado, ou seja, detectaram e toleraram as falhas. As duas arquiteturas agregam características de confiabilidade e disponibilidade a sistemas de controle e apresentam-se como opções promissoras para a gestão de processos em tempo real.

#### **Palavras Chave:**

Tolerância à Falhas, Arquitetura em Anel, Arquitetura TMR, Microcontroladores, PIC, Arquitetura de Computadores, Arquiteturas Tolerantes a Falhas, Controle da Temperatura.

## **Abstract**

The microcontrollers are frequently used in automation and process control. It's a fact that in certain processes the failure in the control system it is inadmissible. In these cases it is necessary to make use of the fault-tolerance techniques. Within this context two fault-tolerant architecture based in microcontrollers were project, built and submitted to extensive tests. The implemented Ring Architecture on the TMR Architecture can endure failure, either in the structure nodes (in the microcontrollers) or in the arches, which represent the connections between the microcontrollers. The nodes are controlled by protocols implemented by a program without the need of a common voting circuit, which is present in the classic TMR Architecture, on any other special circuit to control the redundancy of the circuits. Both system are modules and can operate without one been activated. These allow one module to be removed for maintenance and be reinstalled after words. In tests of physics fault and logic were made in the enveloped architecture and both reacted as expected such as detected and endure fault. Both architecture congregated characteristics of reliability and availability to the control systems.

#### **Key Words:**

Fault Tolerant, Ring Architecture, TMR Architecture, Microcontrollers, PIC, Computer Architecture, Fault Tolerant Architecture, Temperature Control.

## LISTA DE FIGURAS

| Figui | <b>`a</b>                                                              |

|-------|------------------------------------------------------------------------|

| 2.1   | Modelo dos universos de falha, erro e defeito                          |

| 2.2   | Variação típica da taxa de falhas com o tempo                          |

| 2.3   | Estrutura básica de um microcontrolador típico                         |

| 2.4   | Arquitetura Von Neumann: busca e execução de uma instrução             |

| 2.5   | Arquitetura Harvard: busca e execução de uma instrução                 |

| 2.6   | Arquitetura Von Neumann.                                               |

| 2.7   | Arquitetura Harvard                                                    |

| 2.8   | Evolução de vendas                                                     |

| 3.1   | Sistema para controle de temperatura de um ambiente                    |

| 3.2   | Sistema tolerante a falhas para controle da temperatura de um ambiente |

| 3.3   | Arquitetura TMR clássica                                               |

| 3.4   | Fonte de alimentação                                                   |

| 3.5   | Circuito de um módulo das arquiteturas                                 |

| 3.8   | Ambiente MPLAB                                                         |

| 3.6   | Fluxograma do sistema de controle com arquitetura em anel              |

| 3.7   | Fluxograma do sistema de controle com arquitetura em TMR               |

| 3.9   | Fluxo de dados e sinalizadores de erro na arquitetura em anel          |

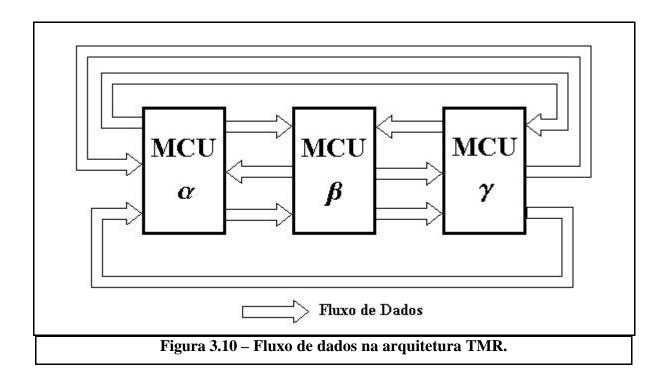

| 3.10  | Fluxo de dados na arquitetura TMR                                      |

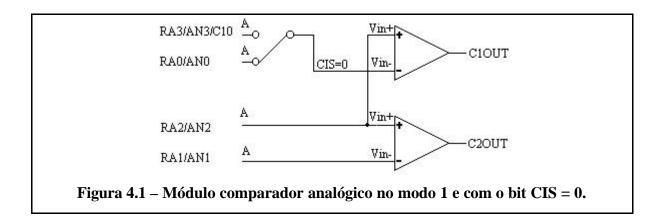

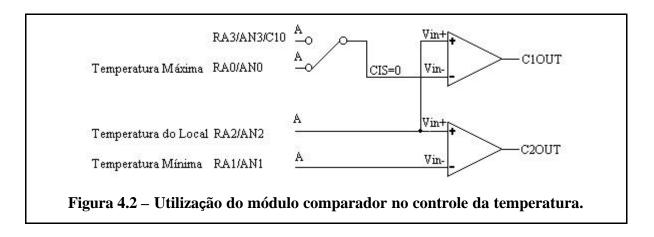

| 4.1   | Módulo comparador analógico no modo 1 e com o bit CIS = 0              |

| 4.2   | Utilização do módulo comparador no controle da temperatura             |

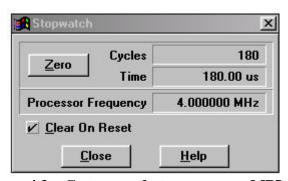

| 4.3   | Contagem de tempo com o MPLAB                                          |

| I.1   | Diagrama de blocos da estrutura interna do PIC 16F628                  |

| I.2   | Memória de programa do PIC 16F628                                      |

| I.3   | Mapa de memória do PIC 16F628                                          |

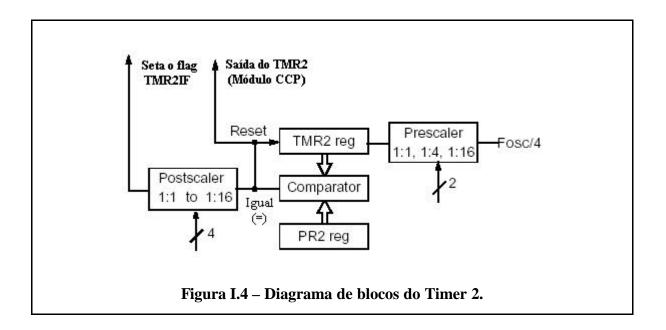

| I.4   | Diagrama de blocos do Timer 2                                          |

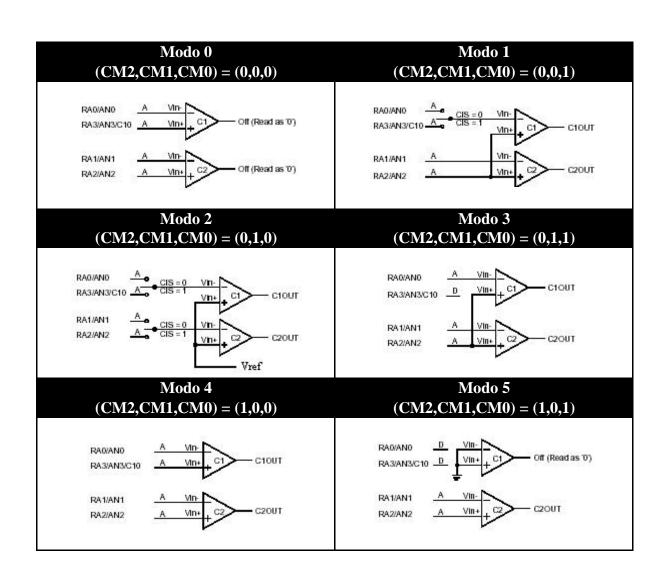

| I.5   | Configurações possíveis para o módulo comparador analógico             |

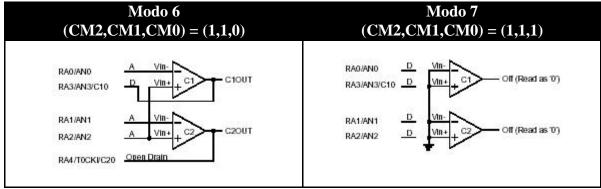

| I.6   | Formatação da palavra de configuração antes da gravação do chip 1      |

| I.7   | Modo ER                                                                |

| I.8   | Modo EC                                                                |

| I.9   | Modos LP, XT e HS                                                      |

## LISTA DE FOTOGRAFIAS

| Fotog | grafia                                                       | pg |

|-------|--------------------------------------------------------------|----|

| 3.1   | Visão geral do protótipo do hardware das arquiteturas        | 29 |

| 3.2   | Visão parcial do protótipo do hardware das arquiteturas      | 29 |

| 3.3   | Visão geral do protótipo das arquiteturas em operação        | 30 |

| 3.4   | Visão parcial do protótipo das arquiteturas em operação      | 30 |

| 3.5   | Primeiro protótipo construído, utilizando MCUs PIC 16F84A    | 31 |

| 3.6   | Protótipo com PIC 16F84A e protótipo com PIC 16F628 e LM35DZ | 31 |

| 3.7   | Gravador μC Flash                                            | 42 |

| 4.1   | Etapa de realização de testes                                | 49 |

| 4.2   | Etapa de simulação de falhas.                                | 49 |

## LISTA DE TABELAS

| Tabe | ela en la companya di managantan di managantan di managantan di managantan di managantan di managantan di manag |

|------|-----------------------------------------------------------------------------------------------------------------|

| 3.1  | Faixa de operação de diferentes modelos de LM35                                                                 |

| 3.2  | Transmissão de dados na arquitetura em anel                                                                     |

| 3.3  | Processo de Votação                                                                                             |

| 3.4  | Transmissão de dados na arquitetura TMR                                                                         |

| 3.5  | Linhas de comando do software para MCU γ                                                                        |

| 3.6  | Linhas de comando do software para MCU $\alpha$ e MCU $\beta$                                                   |

| 4.1  | Relação entre temperatura e sistemas de aquecimento e refrigeração                                              |

| 4.2  | Combinações possíveis entre C1OUT e C2OUT                                                                       |

| 4.3  | Controle da temperatura                                                                                         |

| I.1  | Família PIC 16F62X                                                                                              |

| I.2  | Descrição dos terminais do PIC 16F628                                                                           |

| I.3  | Bits do registrador STATUS                                                                                      |

| I.4  | Seleção do Banco de Memória                                                                                     |

| I.5  | Bits do registrador OPTION                                                                                      |

| I.6  | Ajuste da taxa de divisão do prescaler                                                                          |

| I.7  | Bits do registrador PCON                                                                                        |

| I.8  | Registradores associados ao PORTA                                                                               |

| I.9  | Registradores associados ao PORTB                                                                               |

| I.10 | Bits do registrador INTCON                                                                                      |

| I.11 | Bits do registrador PEI1.                                                                                       |

| I.12 | Bits do registrador PIR1                                                                                        |

| I.13 | Bits do registrador PCL                                                                                         |

| I.14 | Bits do registrador PCLATH                                                                                      |

| I.15 | Seleção de capacitores para o Timer 1                                                                           |

| I.16 | Bits do registrador T1CON                                                                                       |

| I.17 | Seleção do sinal de clock para o Timer 1                                                                        |

| I.18 | Configuração do prescaler do Timer 1                                                                            |

| I.19 | Bits do registrador TMR2CON                                                                                     |

| I.20 | Bits de configuração do Postscaler                                                                              |

| I.21 | Bits de configuração do Prescaler                                                                               |

| Tabe | ela                                                         | pg  |

|------|-------------------------------------------------------------|-----|

| I.22 | Bits do registrador CMCON                                   | 87  |

| I.23 | Configuração do módulo comparador                           | 88  |

| I.24 | Bits do registrador VRCON                                   | 89  |

| I.25 | Valores de saída do módulo VREF para V <sub>DD</sub> = 5V   | 90  |

| I.26 | Bases de tempo para o módulo CCP                            | 91  |

| I.27 | Bits do registrador CCP1CON                                 | 91  |

| I.28 | Exemplos de uso dos bits CCP1X e CCP1Y                      | 92  |

| I.29 | Seleção do modo de operação do Módulo CCP                   | 92  |

| I.30 | Bits do registrador TXSTA                                   | 97  |

| I.31 | Bits do registrador RCSTA                                   | 98  |

| I.32 | Valores de Y para cálculo do Baud Rate                      | 100 |

| I.33 | Bits do registrador EEADR                                   | 100 |

| I.34 | Bits do registrador EECON1                                  | 101 |

| I.35 | Bits de configuração de aspectos do modo de trabalho do PIC | 102 |

| I.36 | Proteção da memória de programa                             | 103 |

| I.37 | Configuração do oscilador interno                           | 103 |

| I.38 | Configuração do oscilador com base na freqüência            | 106 |

## Nomenclatura

## Latinas

| F | Frequência           | Hz   |

|---|----------------------|------|

| I | Corrente elétrica    | A    |

| P | Potência elétrica    | W    |

| R | Resistência elétrica | Ω    |

| T | Temperatura          | [°C] |

| t | Tempo                | S    |

| U | Tensão elétrica      | V    |

## Abreviações

| MCU   | Microcontroller Unit – Unidade de Microcontrolador               |

|-------|------------------------------------------------------------------|

| MODEM | MOdulator/DEModulator-MOdulador/DEModulador                      |

| MTBF  | Mean Time Between Failure – Tempo Médio Entre Falhas             |

| MTTF  | Mean Time To Failure – Tempo Médio Para Ocorrência de Falhas     |

| MTTR  | Mean Time To Repair – Tempo Médio Para Reparo                    |

| NMR   | N Modular Redundancy – Redundância Modular Múltipla              |

| PC    | Program Counter – Contador de Programa                           |

| PIC   | Programmable Integrated Circuit - Circuito Integrado Programável |

| PWM   | Pulse Width Modulation – Modulação de Largura de Pulso           |

| SCI   | Serial Communication Interface – Interface de Comunicação Serial |

| TMR   | Triple Modular Redundancy – Redundância Modular Tripla           |

|       |                                                                  |

## Siglas

| <b>IGCE</b> | Instituto de Geociências e Ciências Exatas    |

|-------------|-----------------------------------------------|

| NASA        | National Aeronautics and Space Administration |

| UNESP       | Universidade Estadual Paulista                |

| UFSCAR      | Universidade Federal de São Carlos            |

## **CAPÍTULO 1**

## INTRODUÇÃO

A dependência humana relacionada aos sistemas computacionais tem sido cada vez maior. Nas telecomunicações, controle de tráfego aéreo e terrestre, armazenamento de dados sigilosos, previsão de tempo, usinas de geração de energia elétrica e em aplicações espaciais, militares, médicas e econômicas, computadores operam ativa e ininterruptamente. É, portanto, necessário que se possa confiar nos serviços prestados pelos mesmos.

Um alto grau de confiabilidade é imprescindível na gestão de tarefas críticas, como no controle de um reator nuclear (CLEMENTS, 1991). O emprego de técnicas de tolerância à falhas, permite agregar altos índices de confiabilidade e disponibilidade a sistemas de computação.

Confiabilidade é definida como a probabilidade de um sistema operar, sem incorrer em falha, até o tempo t, dado que no tempo t = 0, estava funcionando corretamente (HAYES, 1988). É a medida mais utilizada em sistemas em que mesmo curtos períodos de funcionamento incorreto são inaceitáveis, ou em sistemas em que o reparo nem sempre é possível, como em missões não tripuladas e sistemas de aviação (WEBER, 2002.a).

Como disponibilidade, define-se a probabilidade de um sistema estar trabalhando corretamente em um instante de tempo determinado (CLEMENTS, 1991). É a medida de alternância de períodos de operação e reparo de um sistema. Um sistema de computação pode possuir alto grau de disponibilidade, mesmo apresentando períodos de inoperância, desde que esses sejam breves e não comprometam a qualidade do serviço (LAPRIE, 1985).

Esses dois parâmetros são os mais usualmente empregados para mensurar a dependabilidade de um sistema. O termo dependabilidade, segundo Weber (2002.a), "é uma tradução literal do termo inglês **dependability**, que indica a qualidade de um serviço fornecido por um dado sistema e a confiança depositada no serviço fornecido". Outros parâmetros utilizados para medida de dependabilidade são: segurança de funcionamento (*safety*), segurança (*security*), mantenabilidade, testabilidade e comprometimento do desempenho (*performability*) (WEBER, 2002.a).

Existem basicamente duas técnicas utilizadas para implementação de sistemas altamente confiáveis:

- 1- Técnica de prevenção de falhas;

- 2- Técnica de tolerância à falhas.

A primeira procura eliminar as possíveis causas de falhas por construção, através de revisões de projeto e aplicação de métodos de controle de qualidade. A construção de circuitos 100% confiáveis, no entanto, é utopia. Já a segunda técnica, parte do princípio que falhas não podem ser evitadas. Um sistema computacional tolerante a falhas, portanto, pode ser definido como um sistema com alta dependabilidade, capaz de apresentar operação correta, mesmo na presença de falhas. Para se atingir tais metas, os projetos prevêem recursos redundantes, necessários para detectar e mascarar falhas, ou mesmo, isolar ou substituir um elemento com defeito, através de reconfiguração. A redundância – de hardware, software, informação e tempo – é o alicerce da técnica de tolerância à falhas (SIEWIOREK; SWARZ, 1992).

Modelagem de falhas, técnicas de redundância, injeção de falhas e técnicas de tolerância a defeitos para sistemas distribuídos, são áreas já bem desenvolvidas no estudo da tolerância à falhas. Atualmente, pesquisadores se dedicam à construção de sistemas embutidos com alta dependabilidade, através da aplicação de técnicas de tolerância à falhas (RENNELS; HWANG, 2001).

Sistemas embutidos, também conhecidos como sistemas embarcados, são sistemas computacionais dedicados a aplicações específicas, cujas principais características são (Silva Jr; et al., 2002):

- ➤ Alta integração de módulos de hardware e software;

- Voltados para aplicação específica;

- ➤ Interface com o mundo exterior bem definida;

- Restrições e requisitos fortes e bem definidos.

Exemplos de sistemas embutidos são terminais de caixa eletrônico, máquinas de refrigerante, controladores de temperatura, robôs móveis autônomos e aparelhos eletrônicos em geral. Estes sistemas podem ser implementados por meio da construção de hardware específico, baseado em portas lógicas, ou utilizando-se microcontroladores programáveis.

Atualmente, o segundo método é o mais comumente usado, por conferir vantagens como a otimização dos circuitos e custos e proporcionar maior flexibilidade aos sistemas, oferecendo uma melhor relação custo/benefício.

O presente trabalho descreve o projeto, construção e análise de duas arquiteturas microcontroladas tolerantes a falhas, para controle da temperatura de um determinado ambiente. Essas arquiteturas, próprias para utilização em sistemas embutidos, são bastante flexíveis e podem ser facilmente adaptadas para a gestão das mais diferentes tarefas. O trabalho aqui apresentado está estruturado como segue.

O capítulo 2 apresenta uma revisão bibliográfica com enfoque nos principais conceitos e definições relacionados ao estudo de técnicas de tolerância à falhas. A abordagem considera a caracterização de falha, erro e defeito e os vários tipos de

redundância utilizados para obtenção de alta confiabilidade e disponibilidade. As principais características de um microcontrolador são também consideradas neste capítulo.

No capítulo 3, encontra-se a descrição da parte experimental. A implementação do hardware e software das arquiteturas em anel e TMR é tratada, ressaltando-se as diferenças entre elas. Os circuitos e programas necessários para aplicação no controle da temperatura de um ambiente, são apresentados em detalhes.

Os resultados experimentais referentes ao desempenho dos sistemas construídos são apresentados no capítulo 4. Esses resultados são comparados com os obtidos em outras implementações.

As conclusões e sugestões para trabalhos futuros estão contidas no capítulo 5. Subsequentemente, no final do trabalho, encontram-se as referências bibliográficas e os anexos.

## **CAPÍTULO 2**

## REVISÃO DA LITERATURA

#### 2.1 SISTEMAS COMPUTACIONAIS TOLERANTES A FALHAS

## 2.1.1 Introdução

É fato que uma falha em uma máquina algorítmica (BROOKSHEAR, 2000) pode ocorrer a qualquer momento. Sendo assim, é desejável – às vezes imprescindível – que esta possa operar corretamente, mesmo na ocorrência de falhas (CHANDE et al., 1989) (KIMURA et al., 1980).

Com o intuito de se evitar os transtornos advindos de uma pane, são utilizadas basicamente duas técnicas (SIEWOREK; SWARZ, 1982):

- 1- Técnica de prevenção à falhas;

- 2- Técnica de tolerância à falhas.

Com a técnica de prevenção à falhas, que é onerosa, tenta-se prevenir a ocorrência destas, através de revisões de projeto, realização intensa de testes e aplicação de diversos métodos de controle de qualidade. Busca-se eliminar por construção, as possíveis causas de falhas. Todavia, pragmaticamente, não se consegue circuitos 100% confiáveis. Embora seja possível prever a confiabilidade de um lote de componentes, não há como assegurar a confiabilidade de um componente individual (FISCHER, 1990). Projetos que empregam esta técnica, portanto, procuram reduzir a taxa de ocorrência de falhas, a patamares ditos aceitáveis (FRAGA, 1987).

Na técnica de tolerância à falhas, parte-se do princípio que falhas não podem ser evitadas. É escopo desta técnica, reagir à ação da falha na máquina física, permitindo à máquina lógica continuar operando corretamente. Com ela, pode-se construir sistemas com altos índices de confiabilidade e disponibilidade (SIEWOREK; SWARZ, 1982). Em relação à técnica de prevenção à falhas, apresenta a vantagem de permitir a construção de sistemas robustos, com o uso de componentes de menor custo (FISCHER, 1990).

A seguir, são definidos os conceitos de erro, falha e defeito. Posteriormente, são analisadas as expressões de confiabilidade e disponibilidade.

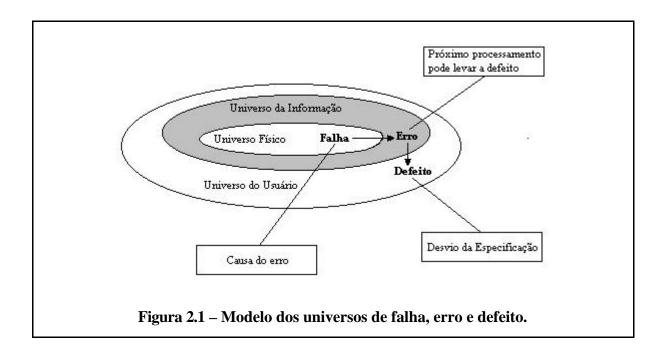

#### 2.1.1 Conceitos de erro, falha e defeito

Autores como Laprie (1985) e Anderson e Lee (1981), ocuparam-se da nomenclatura e dos conceitos básicos da área. Com base em seus trabalhos e concernente ao sucesso de um sistema computacional no atendimento de sua especificação, um defeito (*failure*), trata-se de um desvio da especificação. Não pode ser tolerado, mas deve ser evitado. Um sistema encontra-se em erro, ou em estado errôneo, se o próximo processamento a partir desse estado, pode levar a um defeito. A causa física ou algorítmica de erro, por fim, é denominada falha, conforme mostra a Figura 2.1.

## 2.1.2 Confiabilidade e disponibilidade

Confiabilidade e disponibilidade são medidas probabilísticas, uma vez que a falha é um fenômeno aleatório.

Na equação (2.1), o valor da confiabilidade (R) é dado em função da taxa de falhas (SIEWIOREK; SWARZ, 1992).

$$R(t) = e^{\int_{0}^{t} I(t)d(t)}$$

(2.1)

Nesta equação,  $\lambda$  (t) é a taxa de falhas no intervalo de tempo  $\Delta t$ . A função fornece uma avaliação quantitativa do desempenho de componentes ou sistemas.

A taxa de falhas de componentes é especificada pelo fabricante. Em ensaios laboratoriais, verificam-se quantos dos componentes submetidos aos testes sobreviveram, ou seja, quantos mantiveram operação correta, durante o período de testes. Usualmente, a taxa de falhas é expressa em FITS (uma falha por 10<sup>9</sup> horas) (SIEWIOREK; SWARZ, 1982).

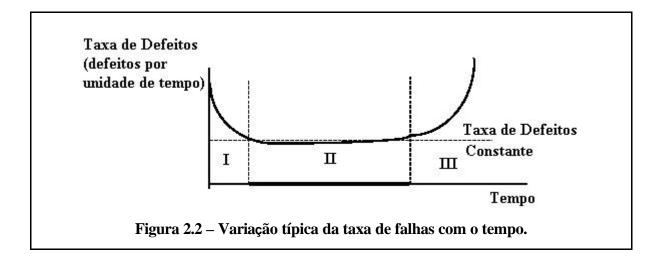

A Figura 2.2 apresenta a variação típica da taxa de falhas com o tempo. Nela, pode-se observar três regiões distintas (HAYES, 1988):

- I- Região de falhas prematuras, com taxa de falhas decrescente. Os componentes apresentam defeito logo após serem postos em funcionamento (mortalidade infantil) (CLEMENTS, 1991).

- II- Região de operação normal, com taxa de falhas praticamente constante.

- III- Região de desgaste, com taxa de falhas crescente. Isso se deve a degradação dos componentes com o decorrer do tempo. Esse período compreende o tempo de vida útil de componentes eletrônicos.

Durante o período de vida útil, a confiabilidade dos componentes individuais é obtida através da equação (2.2).

$$R(T) = e^{-It} (2.2)$$

Circuitos integrados com baixa escala de integração (SSI), têm taxas de falhas de 10<sup>3</sup> a 10<sup>1</sup> FITS, enquanto os com alta escala de integração, da ordem de 10<sup>4</sup> a 10<sup>3</sup> FITS (FISCHER, 1990).

Outros parâmetros relacionados com a confiabilidade de um sistema são (HAYES, 1988):

- ✓ Tempo Médio entre Falhas (MTBF Mean Time Between Failure): indica o tempo médio de funcionamento correto de um sistema reparável, entre sucessivas falhas.

- ✓ Tempo Médio para Ocorrência de Falhas (MTTF Mean Time To Failure): determina, em sistemas não reparáveis, o tempo médio, até a ocorrência da primeira falha.

- ✓ Tempo Médio para Reparo (MTTR Mean Time To Repair): especifica o grau de recuperação ou de conserto do sistema.

O tempo médio entre falhas pode ser obtido com auxílio da equação (2.3). Como se pode notar, o tempo médio entre falhas é igual ao tempo de reparo somado ao tempo médio para ocorrência de falhas.

$$MTBF = MTTR + MTTF (2.3)$$

A disponibilidade traduz a probabilidade de um sistema executar uma tarefa, no instante em que esta é requerida. É usada para medir quão freqüentemente um sistema falha e quão rapidamente é restaurado (SIEWIOREK; SWARZ, 1992). Tanto a equação 2.4 (CLEMENTS, 1991), como a equação 2.5 (HAYES, 1988), podem ser usadas para especificação da disponibilidade (A) de um sistema.

$$A = \frac{MTBF}{MTBF + MTTR} \tag{2.4}$$

$$A = \frac{MTTF}{MTTF + MTTR} \tag{2.5}$$

Em suma, sistemas que devem estar prontos para atender a uma solicitação de serviço a qualquer momento, mas que podem ser paralisados para manutenção e reparo, como sistemas bancários e estações telefônicas, por exemplo, são sistemas onde a disponibilidade é um fator extremamente importante. A confiabilidade, por outro lado, é um requisito imprescindível em sistemas onde o reparo nem sempre é possível, como em satélites espaciais e computadores de bordo.

#### 2.1.3 Utilização de recursos redundantes

A técnica de tolerância à falhas trata-se de um atributo que é designado ao sistema, para se atingir metas de projeto. Conforme já citado, sua função é reagir à ação da máquina física, permitindo a máquina lógica operar corretamente, creditando altos índices de confiabilidade e disponibilidade aos sistemas (AHUJA; MISHRA, 1997). Essa técnica envolve duas etapas (SIEWIOREK, 1992):

- 1- Detecção de erros ou falhas nos sistemas;

- 2- Recuperação do sistema, para que o mesmo continue sua operação normal.

Para que um sistema possa detectar erros ou falhas e tenha a habilidade de se reconfigurar, o mesmo deve possuir recursos redundantes. Esses recursos não são estritamente necessários para o funcionamento de um sistema, mas sim para detecção e tolerância de falhas e reconfiguração (BOTTA, LOPES; 2002). O uso de redundância, na verdade, é o alicerce da técnica de tolerância à falhas. Esta pode apresentar-se em uma das seguintes formas:

- ➤ Redundância de hardware;

- Redundância de software;

- Redundância de tempo;

- Redundância de informação.

A redundância de hardware baseia-se no uso de réplicas de componentes e circuitos. A redução no tamanho dos componentes eletrônicos e seu baixo custo são imensos incentivos para utilização desta técnica (ANISIMOV et al., 2002). No uso de repetição de componentes e circuitos, devem ser considerados fatores como desempenho, tamanho, peso e consumo de energia (CHENG et al., 2000).

A base da redundância de software é a inclusão de recursos de programação, que auxiliam na detecção de erros e recuperação de sistema. Um exemplo simples é incluir num programa, uma rotina para escrever e ler em posições aleatórias da memória, em intervalos de tempo predeterminados (DISHON; GEORGIOU, 1987).

Com a repetição de operações, que implicam na redundância de tempo, pode-se detectar uma possível diferença entre os resultados das mesmas. Isso permite a distinção entre falhas transientes e permanentes. O grande problema desta técnica é que dificilmente, se houver uma falha, ter-se-á todos os mesmos dados para um novo teste (SIEWIOREK; SWARZ, 1982).

A redundância de informação, por sua vez, envolve o uso de informação extra (códigos detectores de erros) na estrutura de dados básica, para detecção e em alguns casos, correção de erros (JOHNSON, 1984). Um dos códigos mais simples e conhecidos é a verificação da paridade (BROOKSHEAR, 2000).

#### 2.1.4 Emprego de sistemas computacionais tolerantes a falhas

As aplicações para sistemas de computação tolerantes a falhas, podem ser classificadas basicamente em quatro categorias:

- ➤ Aplicações de longa duração;

- > Tarefas críticas;

- Adiamento de manutenção;

- ➤ Alta disponibilidade.

Sondas, foguetes, satélites e missões não tripuladas são exemplos de aplicações de longa duração. Algumas devem ter uma probabilidade de operação confiável por períodos tão longos como dez anos. Estes sistemas são altamente redundantes e podem ser reconfigurados automaticamente ou através de estações remotas na Terra.

Aparentemente, as aplicações tolerantes a falhas mais conhecidas, são as referentes à gestão de tarefas críticas. Na execução destas, atrasos e falhas não são tolerados (WENSLEY, 1982). O controle de processos em tempo real, em aeronaves, sistemas militares e certos tipos de controles industriais, são exemplos de tarefas críticas (BUTLER et al., 1985).

Estações localizadas remotamente no espaço, controle de transportes coletivos, como o metrô, e aplicações em ambientes inóspitos, são representantes da categoria de aplicações que requerem adiantamento da manutenção. Neste caso, o sistema deve ser capaz de tolerar as possíveis falhas, que venham a ocorrer, entre uma visita e outra, da equipe responsável pelo reparo.

Um dos parâmetros que deve ser considerado em muitas aplicações, como em atividades comerciais e bancárias, é a disponibilidade. Os usuários destes serviços desejam, e realmente necessitam, de respostas num tempo reduzido, praticamente ao mesmo tempo em que são requisitadas (SIEWIOREK; SWARZ, 1992).

Certamente, quanto maior a dependência humana a sistemas computacionais, maior a necessidade de desenvolvimento de técnicas cada vez mais apuradas de controle de ocorrência de erros. Atualmente, vários pesquisadores, como Rennels e Hwang (2001), se dedicam ao estudo da aplicação de técnicas de tolerância à falhas a sistemas embutidos, baseados em microcontroladores. Subseqüentemente, são consideradas as principais características destes dispositivos.

#### 2.2 MICROCONTROLADORES

#### 2.2.1 Definição

O microcontrolador, também conhecido como computador em um só chip, vem sendo utilizado em escala cada vez maior na automação e controle de processos. Um microcontrolador pode ser definido como um circuito integrado, que contém um processador e seus periféricos típicos. Em virtude de suas dimensões reduzidas, pode ser alojado no próprio produto que gerência, como ocorre no mouse e no teclado, periféricos típicos de um microcomputador (Silva Jr et al., 2002).

Dependendo da aplicação, a Unidade de Microcontrolador (MCU – Micro Controler Unit), deve agregar características diferentes. Deste modo, a escolha de uma MCU deve ser feita com base nos requisitos do sistema (Vaglica; Gilmour, 1990).

Um microcontrolador pode ser classificado de diversas maneiras. A forma mais usual, diz respeito ao barramento de dados. De acordo com esta classificação, um microcontrolador pode se inserir em uma das quatro categorias:

- MCUs de 4 bits;

- MCUs de 8 bits;

- MCUs de 16 bits;

- MCUs de 32 bits.

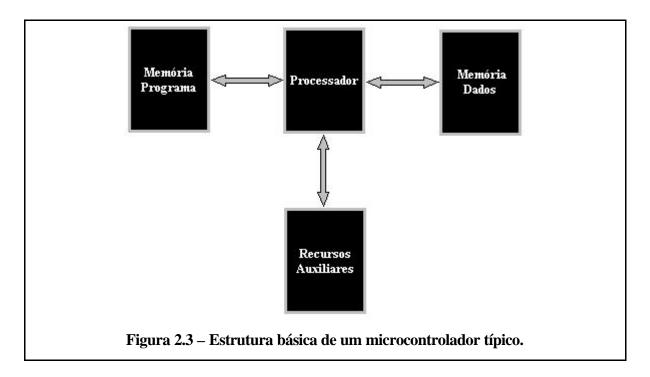

Atualmente, os microcontroladores de 8 bits, são os mais utilizados, devido a seu custo, diversidade e versatilidade. A Figura 2.3 apresenta a estrutura básica de um microcontrolador típico. Como se pode observar, este é composto de:

- Processador;

- Memória de dados;

- Memória de programa;

- > Recursos auxiliares.

O comprimento da palavra armazenada na memória de dados não é necessariamente igual ao da memória de programa. Portanto, cabe ressaltar, que quando se diz que um microcontrolador é de 16 bits, por exemplo, faz-se referência à memória de dados, uma vez que, dependendo da arquitetura do microcontrolador, o tamanho da memória de dados e de programa pode ser diferente, conforme será visto adiante (MICROCHIP, 1997).

#### 2.2.2 Memória de dados

É utilizada para armazenar registradores e variáveis. Permite a escrita e leitura de dados e pode ser de um dos seguintes tipos fundamentais (PEREIRA, 2002):

- ➤ RAM (Ready Only Memory Memória somente para leitura):

Trata-se de uma memória volátil, ou seja, quando o microcontrolador deixa de ser alimentado eletricamente, os dados armazenados nela, são perdidos. Em uma RAM, o processo de leitura e escrita é bastante rápido.

- ➤ EEPROM (Eletrically Erasable Programable Read Only Memory Memória apenas de leitura que se pode programar e apagar eletricamente): A EEPROM é uma memória não volátil, portanto, os dados nela contidos, não são perdidos quando o microcontrolador é desenergizado. O processo de leitura e gravação em uma memória EEPROM é lento.

## 2.2.3 Memória de Programa

É uma memória não volátil (as informações não são perdidas quando o sistema é desligado) que acondiciona as instruções do programa que gerencia uma aplicação. Pode ser de um dos tipos abaixo (NICOLOSI, 2000):

- ➤ ROM (Read Only Memory Memória apenas de leitura) com máscara: As instruções são gravadas nos chips, durante o processo de fabricação e não podem mais ser alteradas ou excluídas. Possuem baixo custo e são viáveis somente para grandes demandas.

- ➤ OTP: Dispositivos fabricados com memória PROM (Programmable Read Only Memory memória apenas de leitura programável), podem ser gravados pelo usuário uma única vez, por intermédio de um gravador ligado a um microcomputador.

- ➤ EPROM (Erasable Programable Read Only Memory Memória apenas de leitura que se pode programar e apagar): As instruções são gravadas como nos dispositivos OTP, com auxílio de um gravador e um microcomputador. Neste caso, porém, as informações podem ser excluídas e gravadas diversas vezes. A exclusão é feita submetendo o chip, que possui em sua face superior uma janela de cristal, a raios ultravioletas.

- ➤ EEPROM (Eletrically Erasable Programable Read Only Memory Memória apenas de leitura que se pode programar e apagar eletricamente): As informações podem ser escritas e apagadas eletricamente, sem a necessidade de raios ultravioletas.

- ➤ FLASH: Como na EEPROM, as informações podem ser excluídas ou escritas eletricamente pelo usuário, utilizando-se um gravador conectado a um microcomputador.

#### 2.2.4 Processador

O Processador ou Unidade Central de Processamento (CPU – Central Processing Unit) é o responsável pela interpretação e execução das instruções do programa (BROOKSHEAR, 2000).

Todo e qualquer processador digital é composto por duas partes, a saber:

- Unidade de Controle: compreende os circuitos que gerenciam todas as atividades do sistema.

- 2- Unidade de Lógica e Aritmética (ULA): possui os circuitos que manipulam os dados.

#### 2.2.5 Recursos Auxiliares

A capacidade de memória e a quantidade de recursos auxiliares determinam a potencialidade e a complexidade de um microcontrolador. Alguns dos recursos auxiliares mais conhecidos são (VAGLICA; GUILMOUR, 1990):

- Conversor Analógico/Digital (A/D) e Digital/Analógico (D/A);

- ➤ Modo de repouso ou de baixo consumo (SLEEP);

- ➤ Portas de I/O (Input/Output Entrada/Saída);

- Cão de Guarda (Watchdog);

- > Temporizadores;

- Canais Seriais;

- > Interrupções.

#### 2.2.6 Arquitetura

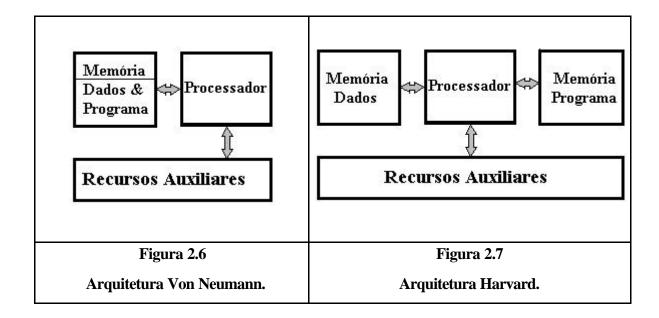

O desempenho de um microcontrolador depende muito de sua arquitetura interna. As arquiteturas de computadores mais populares são a Von Neumann, com conjunto de instruções complexas (CISC – Complex Instruction Set Computer) e a Harvard, com conjunto reduzido de instruções (RISC – Reduced Instruction Set Computer).

O popular microcontrolador 8051 (INTEL, 2002), fabricado pela Intel, é um exemplo de dispositivos CISC, enquanto que os microcontroladores PIC (MICROCHIP, 1997), fabricados pela Microchip, e os AVR (ATMEL, 2002.a) (ATMEL, 2002.b), fabricados pela Atmel, são exemplos de dispositivos RISC. A Atmel produz também, assim como outras empresas, dispositivos CISC, compatíveis com a família 8051 (SCHUNK, 2001) (ATMEL, 2002.c).

| 1°              | 2°               | 3°              | 4°               |

|-----------------|------------------|-----------------|------------------|

| Ciclo Instrução | Ciclo Instrução  | Ciclo Instrução | Ciclo Instrução  |

| Fase de Busca   | Fase de Execução | Fase de Busca   | Fase de Execução |

| 1ª Instrução    | 1ª Instrução     | 2ª Instrução    | 2ª Instrução     |

Figura 2.4 – Arquitetura Von Neumann: busca e execução de uma instrução.

| 1°              | 2°               | 3°               | <b>4</b> °       |

|-----------------|------------------|------------------|------------------|

| Ciclo Instrução | Ciclo Instrução  | Ciclo Instrução  | Ciclo Instrução  |

| Fase de Busca   | Fase de Execução |                  |                  |

| 1ª Instrução    | 1ª Instrução     |                  |                  |

|                 | Fase de Busca    | Fase de Execução |                  |

|                 | 2ª Instrução     | 2ª Instrução     |                  |

|                 |                  | Fase de Busca    | Fase de Execução |

|                 |                  | 3ª Instrução     | 3ª Instrução     |

|                 |                  |                  | Fase de Busca    |

|                 |                  |                  | 4ª Instrução     |

Figura 2.5 – Arquitetura Harvard: busca e execução de uma instrução.

Uma vantagem dos dispositivos RISC, em relação aos CISC, é a velocidade de execução de programas. Uma desvantagem, é que operações matemáticas, são mais facilmente executadas por dispositivos CISC (SCHUNK, 2001).

Na arquitetura creditada a John von Neumann (talvez incorretamente<sup>1</sup>), existe um único barramento entre memórias e CPU, por onde trafegam dados e instruções. Já na arquitetura Harvard, existem barramentos independentes, um para dados e outro para instruções. Isto permite que dados e instruções tenham comprimentos diferentes. Além disso, viabiliza o uso da técnica denominada pipelining, que possibilita que as fases de busca e execução de uma

.

<sup>&</sup>lt;sup>1</sup> "Alguns reivindicam que esta idéia foi desenvolvida originalmente por J. P. Eckert, Jr., na Moore School, mas suas idéias resultaram de uma pesquisa em grupo, tendo sido, no final, indevidamente atribuída a von Neumann" (BROOKSHEAR, 2000).

instrução ocorram simultaneamente. Assim, enquanto na arquitetura Von Neumann, a busca e execução de uma instrução são realizadas seqüencialmente (Figura 2.4), na arquitetura Harvard, enquanto uma instrução é executada, outra é buscada na memória (Figura 2.5). Pragmaticamente, portanto, microcontroladores construídos com arquitetura Harvard e tecnologia RISC, são mais rápidos que os construídos com arquitetura Von Neumann e tecnologia CISC. Como exemplo, o popular 8051 da Intel, rodando a 12MHz, executa a maioria das instruções em lµs, enquanto um PIC da Microchip, executa a maioria de suas instruções em 1µs rodando a 4MHz (VIDAL, 1997).

A Figura 2.7 mostra a estrutura básica de um microcontrolador construído com arquitetura Harvard, ao passo que a Figura 2.6, apresenta a de um microcontrolador com arquitetura Von Neumann. É conspícuo, que para um microcontrolador com arquitetura Von Neumann, existe uma memória única, onde são armazenados dados e instruções, ao passo que, em um microcontrolador com arquitetura Harvard, a memória onde são gravadas as instruções (memória de programa), é distinta da memória onde são armazenados os dados.

### 2.2.7 Seleção de um Microcontrolador

A maioria dos fabricantes de circuitos integrados possui sua linha de microcontroladores, tendo em vista a crescente demanda por tais dispositivos. Não existe, porém, uma MCU que possa ser considerada "a melhor entre todas". No momento da escolha, há que se levar em conta que para cada aplicação, existe um modelo que pode oferecer a melhor relação custo/benefício (VAGLICA; GUILMOUR, 1990). Abaixo estão alistados aspectos que devem ser observados:

- Velocidade de execução das instruções;

- Capacidade da memória de programa;

- Número de portas de entrada e saída;

- Tamanho da memória de dados;

- Periféricos inclusos:

- Restrições impostas pelo sistema, como consumo de energia, faixa de temperatura e tipo de encapsulamento.

Para as arquiteturas tolerantes a falhas descritas neste trabalho, foram usados microcontroladores PIC (Programmable Integrated Circuit – circuito integrado programável), fabricados pela Microchip.

Esta empresa, cuja matriz localiza-se em Chandler, Arizona, oferece atualmente, mais de uma centena de modelos de microcontroladores. Isso facilita encontrar modelos que atendam aos requisitos das mais diferentes aplicações. Outra vantagem, de se trabalhar com a família de microcontroladores PIC, é a facilidade encontrada na migração de um modelo para outro, uma vez que todos os modelos conservam certas características básicas e possuem um set de instruções bem parecido (MICROCHIP, 1997) (SOUZA, 2000). Hoje, em sua linha de produtos, encontram-se os controladores digitais de sinais (DSC – Digital Signal Controller), numa analogia aos processadores digitais de sinais (DSP – Digital Signal Processor). São dispositivos com memória de programa de 24 bits e longitude de dados de 16 bits.

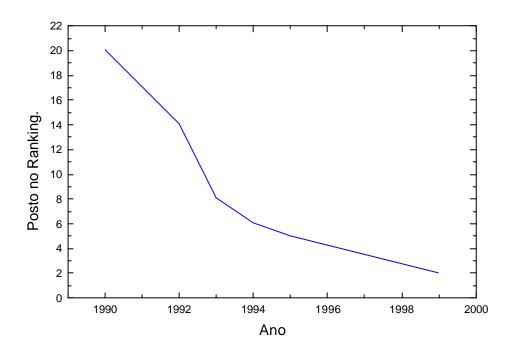

Os microcontroladores PIC obtiveram ampla aceitação no mercado mundial. Uma evidência disso, é sua rápida ascensão no ranking mundial de vendas de microcontroladores de 8 bits. Conforme mostra a Figura 2.8, em 1990, a Microchip ocupava o vigésimo posto; em 1999, o segundo.

Figura 2.8 – Evolução de vendas.

Fatores que levaram a opção por tais dispositivos, estão alistados a seguir:

- Ampla variedade de modelos;

- > Farta informação bibliográfica;

- > Excelente relação custo/benefício;

- Facilidade de migração de um modelo para outro;

- Ferramentas de desenvolvimento econômicas e fáceis de manejar;

- Velocidade de execução de programas superior a dos principais concorrentes;

- O tamanho do código que seus programas geram é menor que dos principais concorrentes.

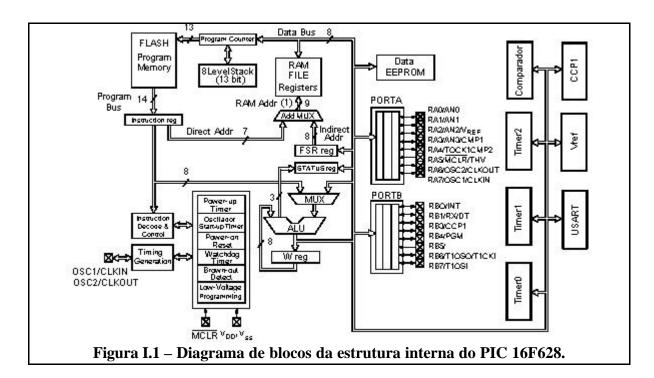

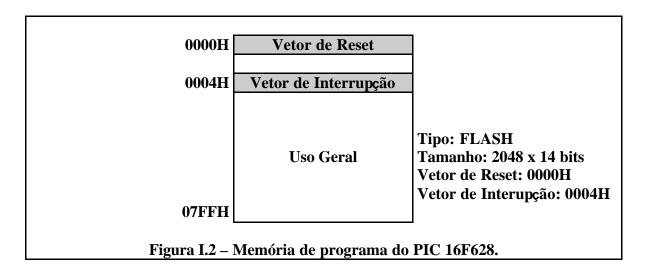

Dentre mais de setenta modelos que compõem a gama média (MICROCHIP, 1997), ou família intermediária, de microcontroladores da Microchip, o PIC 16F628 (MICROCHIP, 1999), que é analisado no Anexo I, foi eleito por possuir características tais, que atende aos requisitos da aplicação em questão (controle da temperatura), oferecendo excelente relação custo/benefício.

#### Algumas características do PIC 16F628 (MICROCHIP, 1999) são:

- Memória de programa FLASH com capacidade para 2048 instruções de 14 bits;

- ➤ Memória de dados EEPROM com capacidade para 128 palavras de 8 bits;

- Microcontrolador de 18 pinos, o que facilita a construção de protótipos;

- ➤ Memória de dados RAM com capacidade para 224 palavra x 8 bits;

- ➤ Comparadores analógicos com referência programável de tensão;

- Capacidade de corrente de 25mA por pino de I/O;

- Módulo de Captura, Comparação e PWM;

- Canal de comunicação serial USART;

- Dez fontes possíveis de interrupção;

- Possui 16 portas de entrada e saída;

- ➤ Temporizadores/Contadores;

- Oscilador interno;

- Watchdog.

O capítulo seguinte relata a construção das arquiteturas tolerantes a falhas para controle da temperatura, onde os microcontroladores PIC 16F628 foram usados.

# **CAPÍTULO 3**

## PARTE EXPERIMENTAL

# 3.1 MODELAGEM TEÓRICA

# 3.1.1 Introdução

Os microcontroladores são dispositivos eletrônicos largamente utilizados em aplicações de controle e automação, tais como: controle de motores, edifícios inteligentes, instrumentação eletrônica, visão computacional, sistemas de comunicação, controle de aplicações aeroespaciais, navegação por satélite, controle de periféricos de microcomputadores, sistemas de segurança, equipamentos hospitalares e robótica.

Levando em conta que na gestão de certos processos, a falha do sistema de controle é inadmissível, podendo implicar em consequências drásticas, foram projetadas duas arquiteturas tolerantes a falhas usando microcontroladores, a Arquiteturas TMR e a Anel. Ambas são capazes de tolerar falhas tanto nos nodos da estrutura, ou seja, nos microcontroladores, como nos arcos (FILHO; NUNES, 1995), que representam as ligações entre os mesmos.

A diferença entre a arquitetura em anel com três módulos e a TMR, aqui apresentadas, está no programa de gerenciamento. Deste modo, um mesmo circuito serve de base para operação de ambas as arquiteturas.

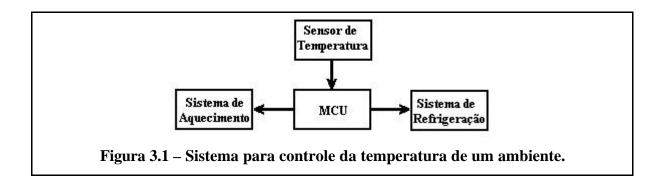

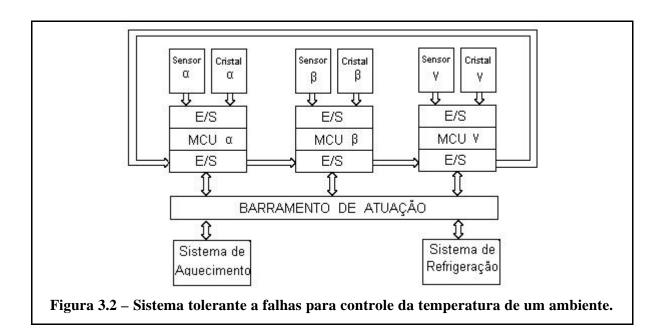

A Figura 3.1 mostra um sistema simplex (arquitetura sem recursos de tolerância à falhas) para controlar a temperatura de um ambiente. Para manter a temperatura do ambiente dentro da faixa desejada, um sensor irá monitorá-la e informará constantemente as variações a um microcontrolador, responsável pelo controle do processo, para que este atue sobre um sistema de aquecimento ou de refrigeração, se necessário. É certo que uma falha no sensor ou no microcontrolador, pode levar a temperatura do ambiente a índices indesejados. Se o sistema, no entanto, for tolerante a falhas, a situação será outra. A Figura 3.2 apresenta um sistema tolerante à falhas, para controle da temperatura de um ambiente.

Ao invés de um sensor para monitorar as mudanças de valor da temperatura, existem agora três. O mesmo ocorre com o número de MCUs. Os microcontroladores recebem informação de sensores diferentes e comunicam-se para verificar se há algum sensor com defeito e qual dos módulos será responsável pelo controle do sistema, ou seja, qual deles atuará sobre o sistema de refrigeração ou aquecimento. Desta forma, mesmo que ocorra falha em um dos microcontroladores ou em um dos sensores, o sistema de controle continuará operando corretamente. Logo, a técnica de tolerância à falhas agrega maior confiabilidade ao sistema de controle. Além disso, se ocorrer falha em um dos módulos, o mesmo poderá sofrer intervenção da manutenção sem implicar na desativação do sistema de controle, pois os demais módulos podem garantir a disponibilidade do serviço de controle da temperatura (BOTTA; LOPES, 2002.a).

## 3.1.2 Arquiteturas TMR e Anel

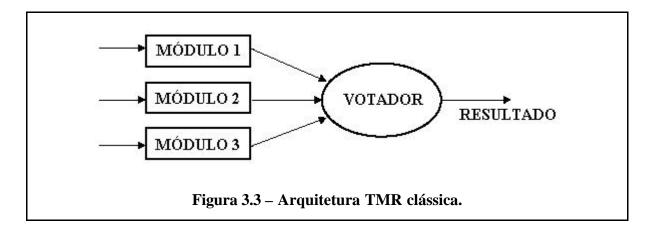

Três módulos trabalhando em sincronismo e executando as mesmas tarefas, com os resultados de cada módulo sendo submetidos a um único circuito votante por maioria (geralmente implementado por hardware), como mostra a Figura 3.3, constitui uma arquitetura TMR clássica. Uma saída permanece válida, desde que dois dos três módulos concordem e o circuito de votação esteja livre de falhas (HAYES, 1988). Os circuitos votantes podem ser implementados com a técnica de prevenção à falhas. Esta arquitetura suporta falhas em apenas um módulo. Uma extensão desta, é a arquitetura com redundância modular múltipla (NMR – N MODULAR REDUNDANCY), que pode suportar falhas em f módulos, onde N = 2f + 1 (SIEWIOREK; SWARZ, 1992). Na implementação aqui descrita, foi eliminado o circuito votante comum e a votação é executada por software. Quando um dos microcontroladores apresenta defeito, o sistema continua exercendo a tarefa de controle, desde que os outros dois módulos funcionem corretamente (BOTTA; LOPES, 2002.a).

A arquitetura em anel, (RODA, 1983), é um tipo de estrutura NMR, onde os módulos estão configurados num loop (anel) e sem circuito votante comum. Cada módulo recebe os dados de uma fonte, processa-os e envia o resultado do processamento para os outros módulos através de um canal de comunicação, havendo circulação dos dados através do anel. A circulação pode ser unidirecional ou bidirecional, podendo até

mesmo usar canais redundantes. Uma vez que os módulos têm dados suficientes, cada módulo executa a votação por programação, em concordância com um determinado algoritmo. O resultado da votação é indicado através de sinalizadores de erro que são utilizados para selecionar apenas um módulo (sem falhas), para dar saída ao sistema (FISCHER, 1990). A Figura 3.2 mostra uma estrutura em anel com três módulos e circulação unidirecional no sentido horário. Para votação dos dados podem ser usadas duas estratégias:

- 1- Votação majoritária: sobre todos os dados;

- 2- Votação sobre um número parcial de dados.

No primeiro caso, cada módulo recebe os dados de todos os outros para votação. No outro, a votação é feita sobre um número menor de dados, sendo que o limite, é a comparação de dados de dois módulos adjacentes.

A confiabilidade da arquitetura em anel foi analisada<sup>1</sup> levando-se em consideração:

- 1- Número de módulos:

- 2- Estratégia de votação.

Foram obtidas as seguintes conclusões:

- 1- Com o uso da estratégia de votação sobre a maioria dos dados, a confiabilidade decresce conforme aumenta o número de módulos.

- 2- Usando a estratégia de votação sobre um número parcial de dados, quando o número de dados é reduzido, há um aumento de confiabilidade.

<sup>&</sup>lt;sup>1</sup> As limitações da arquitetura em anel com mais de três módulos e as expressões de confiabilidade para o sistema com estratégia de votação majoritária e parcial, podem ser encontradas, pelos leitores interessados, nos trabalhos realizados por Roda (1983) e Fischer (1990).

3- A arquitetura em anel, com três módulos, utilizando a estratégia de votação sobre um número parcial de dados, têm os mesmos valores de confiabilidade que a arquitetura TMR.

Com base no acima exposto, para implementação da arquitetura em anel apresentada neste trabalho, foi usada a estratégia de votação sobre um número parcial de dados.

Subsequentemente, serão consideradas as implementações de hardware e software, das arquiteturas tolerantes a falhas, para controle da temperatura de um determinado ambiente.

# 3.2 ANÁLISE EXPERIMENTAL

### 3.2.1 Hardware dos sistemas

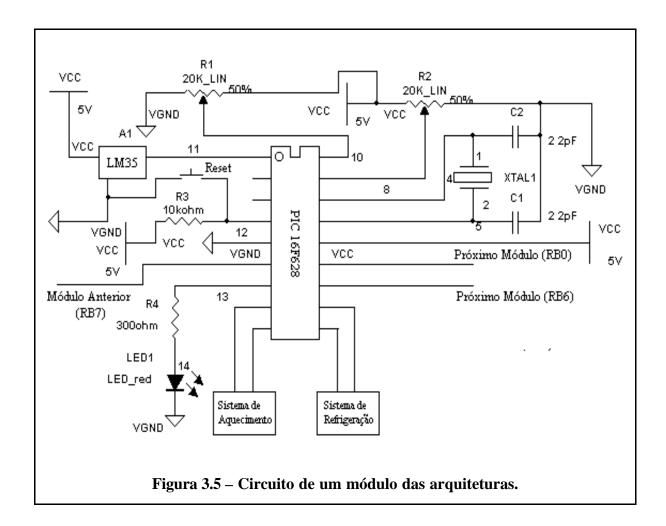

Foi projetado e construído um circuito que pudesse suportar tanto a arquitetura em anel como a TMR, apresentadas nesse trabalho $^2$ . O circuito implementado é composto de três módulos idênticos, que se comunicam por intermédio das portas de entrada e saída dos microcontroladores. Cada módulo é constituído basicamente por fonte de alimentação (5 $V_{CC}$ ), cristal oscilador (4MHz), sensor de temperatura e microcontrolador.

Para maiores detalhes, deve-se reportar aos trabalhos de Roda (1983) e Fischer (1990).

٠

<sup>&</sup>lt;sup>2</sup> Isso foi possível devido à arquitetura em anel implementada ser composta por três módulos. Caso bssem construídas com mais de três, o circuito seria diferente para o sistema NMR-anel e NMR-mascarável, devido à forma de comunicação entre os módulos.

Para a aplicação destas arquiteturas, na gestão da temperatura de um determinado ambiente, foram utilizados microcontroladores PIC16F628, devido a este modelo possuir comparadores analógicos internos. Os sensores de precisão LM35 (NATIONAL, 2000), foram os selecionados para detecção das variações de temperatura. Estes dispositivos fornecem em um de seus terminais uma tensão elétrica, cujo valor, é de 10mV/°C, linear em toda a faixa de operação, que vai de – 55 a +150°C (NATIONAL, 2000). Desta forma, V<sub>OUT</sub> é 300, –100, e 1200mV a 30, –10 e 120°C, respectivamente. Sendo o consumo destes sensores de 60μA, o calor gerado no próprio dispositivo pode ser considerado desprezível, o que significa que praticamente não influi na medida. A Tabela 3.1 apresenta a faixa de operação de diferentes modelos de LM35. O modelo utilizado neste trabalho foi o LM35DZ (a última letra, no caso a letra Z, se refere ao tipo de encapsulamento do dispositivo).

Tabela 3.1 – Faixa de operação de diferentes modelos de LM35.

| Modelo       | Faixa de Operação |

|--------------|-------------------|

| LM35/LM35A   | -55 a +150°C      |

| LM35C/LM35CA | -40 a +110°C      |

| LM35D        | 0 a +100°C        |

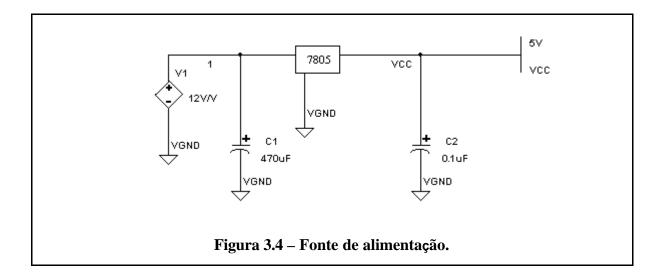

Um circuito bastante simples, com base no circuito integrado 7805, foi utilizado para implementação das fontes de alimentação estabilizadas. O diagrama da fonte pode ser visto na Figura 3.4.

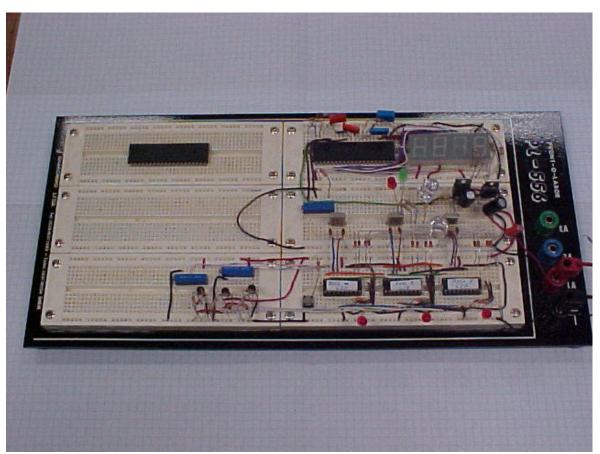

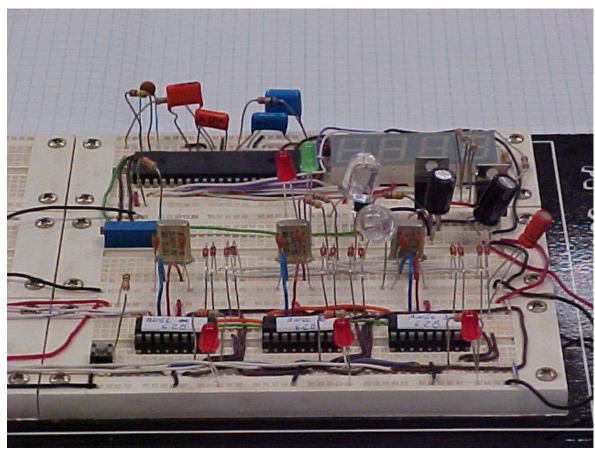

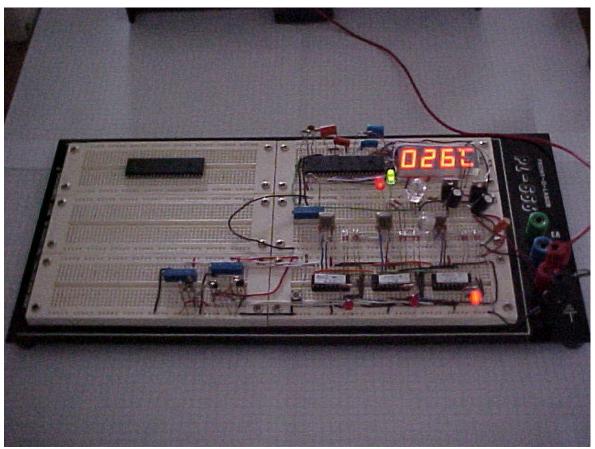

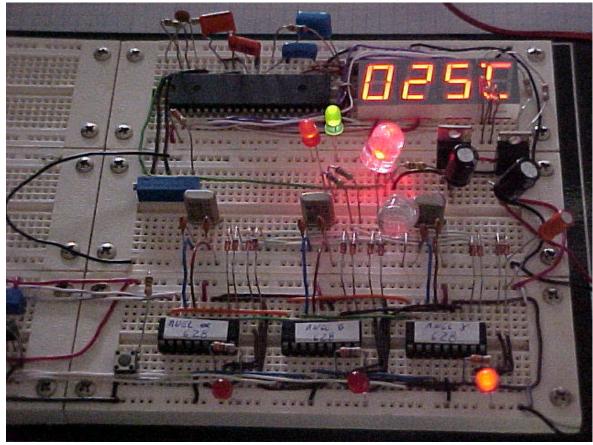

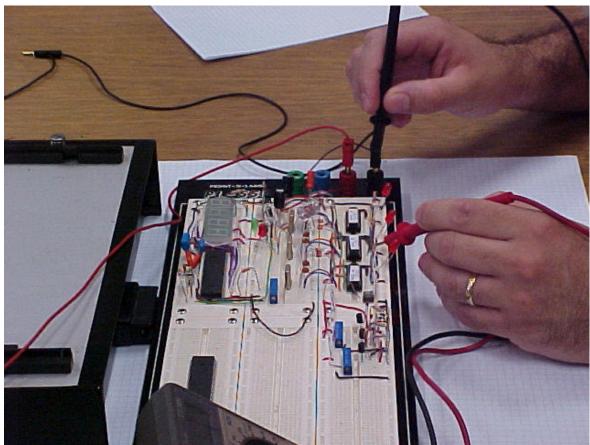

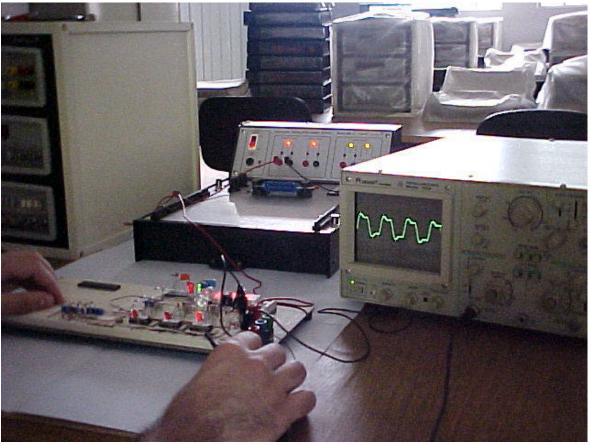

O diagrama do circuito de um módulo, das arquiteturas implementadas, é apresentado na Figura 3.5. Já nas Fotografias 3.1, 3.2, 3.3 e 3.4, é possível observar o protótipo das arquiteturas tolerantes a falhas, para gestão da temperatura de um determinado ambiente.

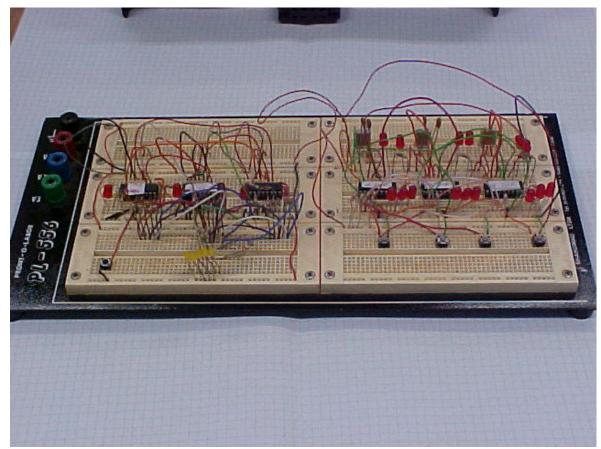

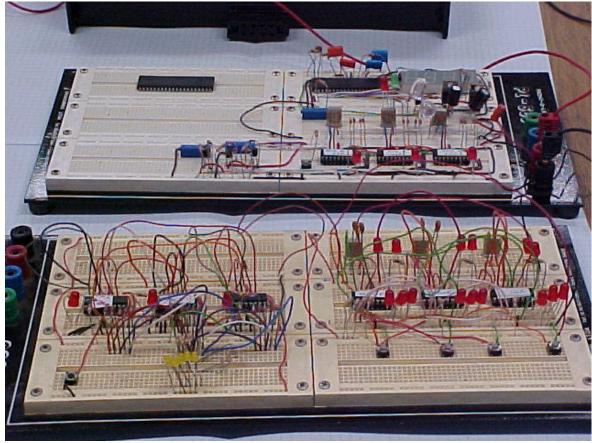

As arquiteturas aqui descritas foram originalmente construídas com MCUs PIC16F84A (MICROCHIP, 2001.b), como mostram as Fotografias 3.5 e 3.6. De início, foram construídas para propósito geral, sendo que, os microcontroladores recebiam 5 bits e representavam o valor destes por meio de LEDs. Embora já tenha sido mencionado, vale lembrar que uma grande vantagem de se trabalhar com a família de microcontroladores PIC, é que todos os modelos possuem um conjunto de instruções bem parecido, além de manterem muitas semelhanças entre suas características básicas (SOUZA, 2000). Isto facilita muita a migração de um modelo para outro.

Fotografia 3.1 – Visão geral do protótipo do hardware das arquiteturas.

Fotografia 3.2 – Visão parcial do protótipo do hardware das arquiteturas.

Fotografia 3.3 – Visão geral do protótipo das arquiteturas em operação.

Fotografia 3.4 – Visão parcial do protótipo das arquiteturas em operação.

Fotografia 3.5 – Primeiro protótipo construído, utilizando MCUs PIC 16F84A.

Fotografia 3.6 – Protótipo com PIC 16F84A e protótipo com PIC 16F628 e LM35DZ.

#### 3.2.2 Software dos sistemas

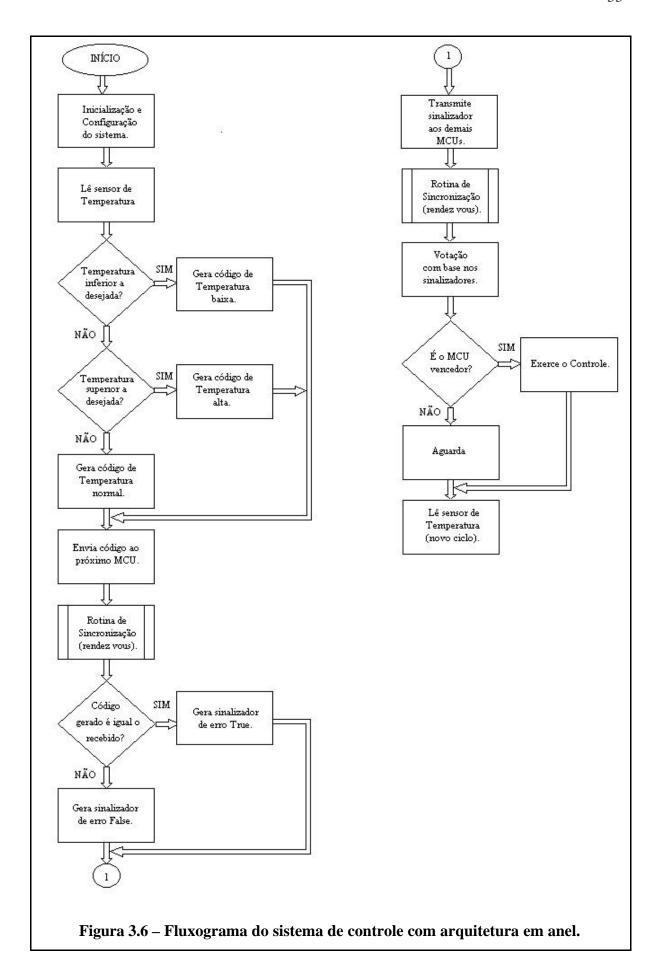

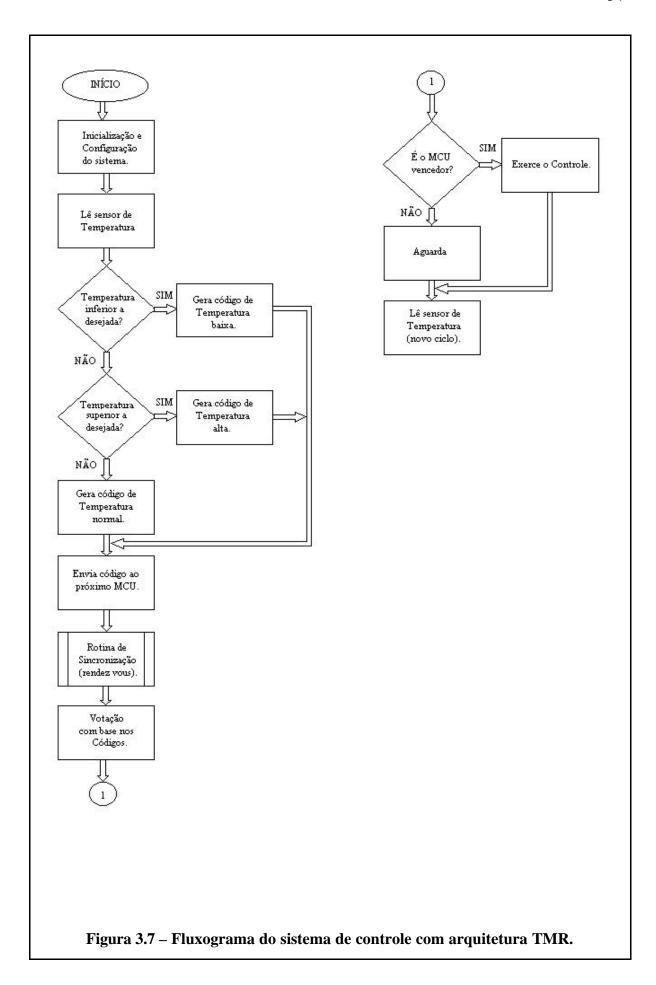

Nos fluxogramas das Figuras 3.6 e 3.7, demonstra-se à maneira como funcionam os sistemas de controle com arquitetura em anel e TMR, respectivamente.

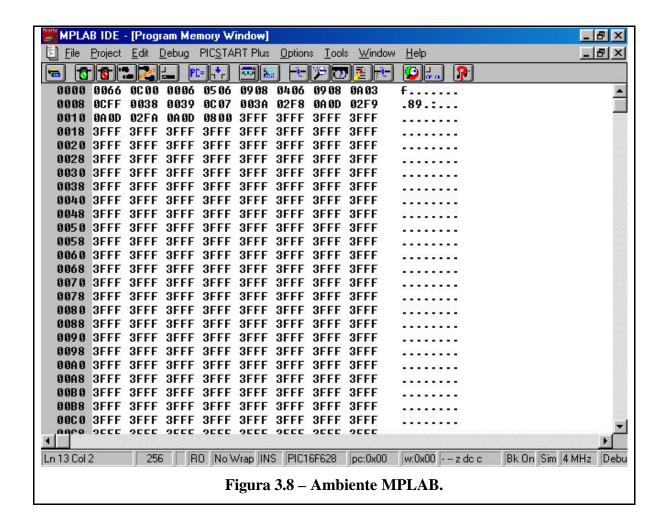

Os programas desenvolvidos foram escritos em linguagem assembly e podem ser alterados para a construção de sistemas com um maior números de módulos e/ou para o controle das mais diferentes tarefas. Para criação dos programas, foi utilizado o MPLAB (MICROCHIP, 2001), um ambiente integrado de programação (IDE), que contém módulos de edição, montagem e simulação de programas para microcontroladores PIC. Para uso da linguagem assembly, o MPLAB dispõe de um montador (assembler), denominado MPASM (PEREIRA, 2002). O ambiente MPLAB pode ser visto na Figura 3.8.

Cada MCU possui uma cópia do programa desenvolvido, gravado em sua memória de programa. A seguir, é comentada a forma como os programas são estruturados para as diferentes arquiteturas.

## 3.2.3 Estrutura do software da arquitetura em anel

1) Inicialização: O PIC 16F628 dispõe de muitos recursos. Neste ponto é feita a configuração da maneira como ele irá trabalhar (utilizando o circuito oscilador interno ou um externo, quais portas serão utilizadas como entrada e quais serão utilizadas como saída, fontes de interrupção que estarão ativas, enfim, a configuração dos periféricos internos) e a alocação de registradores de propósito geral (GPR) para variáveis, constantes e flags que serão utilizados pelo sistema.

2) Aquisição e interpretação de dados: O sensor de temperatura é lido e é verificado se a temperatura está entre os limites desejados. Cada microcontrolador gera seu parecer.

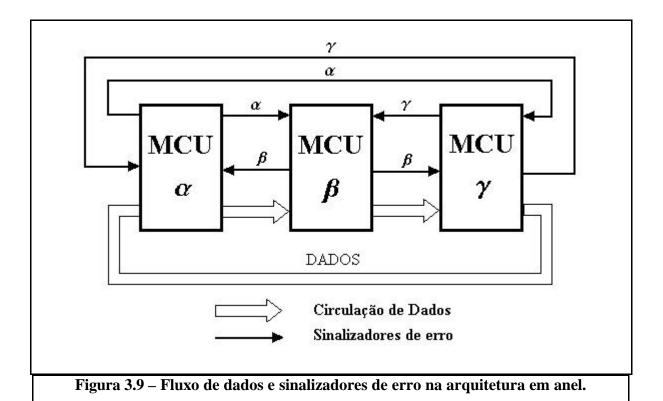

3) Transmissão de dados: A Figura 3.9 mostra a circulação dos dados no anel. Cada microcontrolador se comporta na transmissão de dados, em conformidade com a Tabela 3.2.

Tabela 3.2 – Transmissão de dados na arquitetura em anel.

| Transmissão | MCUa      | MCUß      | MCU?      |

|-------------|-----------|-----------|-----------|

| 1° Ciclo    | Transmite | Recebe    | Aguarda   |

| 2º Ciclo    | Aguarda   | Transmite | Recebe    |

| 3º Ciclo    | Recebe    | Aguarda   | Transmite |

- 4) Comparação dos dados e geração do sinalizador de erro: Os microcontroladores comparam seu próprio parecer com o que recebeu. Com base na comparação, geram um sinalizador de erro.

- 5) Transmissão do sinalizador de erro: Cada microcontrolador recebe o sinalizador de erro dos outros dois, como mostra a Figura 3.9. Esse sinalizador é constituído de 8 bits e transmitido serialmente aos outros módulos.

- 6) Processo de votação: De posse do código de erro dos outros dois módulos, cada MCU consulta uma tabela (Tabela 3.3) para saber se é o vencedor, ou seja, se fará o controle do sistema. Para qualquer outra combinação não apresentada nesta tabela, nenhum microcontrolador exercerá a função de controle e os sistemas de aquecimento e refrigeração permanecerão desligados.

Tabela 3.3 – Processo de Votação.

| Módulo a  | Módulo ß  | Módulo?   | Vencedor |

|-----------|-----------|-----------|----------|

| Sem Falha | Sem Falha | Sem Falha | MCU?     |

| Sem Falha | Sem Falha | Com Falha | MCUß     |

| Sem Falha | Com Falha | Sem Falha | MCUa     |

| Com Falha | Sem Falha | Sem Falha | MCU?     |

7) Controle pelo módulo vencedor: O módulo vencedor dá saída ao sistema, ou seja, atua sobre o sistema de refrigeração ou de aquecimento, conforme a necessidade.

# 3.3.3 Estrutura do software da arquitetura TMR

- 1) Inicialização: Análoga à arquitetura em anel.

- 2) Aquisição e interpretação de dados: Da mesma forma que a arquitetura em anel.

- *3) Transmissão de dados:* A Figura 3.10 demonstra a comunicação entre MCUs na arquitetura TMR. Cada microcontrolador transmite seu parecer aos demais módulos, conforme a Tabela 3.4.

- 4) Comparação dos dados: Cada microcontrolador compara seu parecer com o dos outros dois e gera flags internos, que são utilizados no processo de votação.

- 5) Processo de votação: Com base nos flags gerados, cada MCU consulta uma tabela (Tabela 3.3) para saber se é o vencedor, ou seja, se fará o controle do

sistema. Para qualquer outra combinação não apresentada na Tabela 3.3, nenhum microcontrolador exercerá a função de controle e os sistemas de aquecimento e refrigeração ficarão desligados.

6) Controle pelo módulo vencedor: Mesmo procedimento da arquitetura em anel.

Transmissão MCUa **MCU**ß MCU? 1º Ciclo Transmite Recebe Recebe 2º Ciclo Recebe Transmite Recebe 3° Ciclo Recebe Recebe Transmite

Tabela 3.4 – Transmissão de dados na arquitetura TMR.

#### 3.3.4 Considerações sobre os sistemas

- a) Os três microcontroladores operam de forma concorrente, pois, a votação deve ser sobre a mesma versão de dados. Para sincronizá-los, foi usada a técnica de "rendez-vous" (WENLEY, 1983.a), também chamada de "ponto comum de encontro". O ponto de encontro, neste caso, é o ponto no processo onde cada módulo apronta o dado para ser submetido à votação. Neste esquema, o módulo que chega primeiro ao "ponto de encontro", avisa os outros e fica esperando pela chegada dos demais. Após este encontro, todos executam a votação em paralelo (WENLEY, 1983.b).

- b) Se um módulo é retirado do sistema, para reparo ou outro motivo, o sistema considera o módulo ausente como um módulo falho.

- c) Após a obtenção de todos os resultados (leitura do sensor, interpretação e comparação de dados), o sistema primeiro verifica a presença de falhas para depois exercer a ação de controle (BOTTA; LOPES, 2002.a). Os chamados "testes de último momento", têm a vantagem de testar todas as atividades do sistema (LOMBARDI; RODA, 1982).

### 3.3.5 A diferença entre o software das arquiteturas implementadas

Sob este tópico, são expostas algumas peculiaridades dos programas desenvolvidos e a diferença existente entre os programas para a arquitetura em anel e TMR.

"Para que um programa seja escrito e funcione corretamente", segundo Souza (2000), "basta que as instruções certas sejam colocadas na ordem correta". Embora isso seja verdade, um programa que não é bem estruturado, mesmo sendo funcional, não pode ser considerado eficiente. De acordo com o próprio Souza (Souza, 2000), "isto porque ele não estará devidamente estruturado e padronizado, dificultando futuras alterações e/ou o entendimento por outros programadores". Assim sendo, houve a preocupação com a obtenção de uma estruturação adequada, separando e identificando nos programas, cada tarefa.

Falando ainda sobre padronização e otimização da programação, não se pode deixar de mencionar os arquivos de definições. Esses arquivos, denominados "Includes" pela Microchip, são arquivos de texto ou código fonte, que podem ser incluídos em um programa, com a finalidade de evitar digitações desnecessárias. A Microchip disponibiliza um arquivo de definições para cada modelo de microcontrolador. Nesses arquivos, encontra-se a definição dos nomes e endereços de cada SFR, além de outras definições necessárias para o uso de um microcontrolador. O arquivo include para o PIC 16F628 (PIC 16F628.INC) pode ser apreciado no Anexo II.

Com o intuito de facilitar ainda mais a compreensão dos programas, praticamente todas as linhas de comando foram comentadas, sendo os comentários encontrados logo após um ponto-e-vírgula (;). Cabe aqui a menção, que os comentários não ocupam espaço em um arquivo executável (.hex), somente no código fonte (.asm). Isso se deve ao fato, de os comentários serem ignorados pelo compilador no processo de geração do arquivo executável.

Uma observação atenta das listagens dos programas, para a arquitetura em anel e TMR, revela que a diferença entre os programas para as diferentes arquiteturas

encontra-se na rotina principal. Como já foi ressaltado, a diferença fundamental entre as arquiteturas, está no método de comunicação entre os módulos do sistema, conforme é possível notar com a ajuda das Figuras 3.9 e 3.10. Além da diferença entre a circulação de dados na arquitetura em anel e o fluxo de dados na TMR, existem os sinalizadores de erro. A arquitetura TMR não utiliza tais sinalizadores, ao passo que a arquitetura em anel emprega-os. Deste modo, para a arquitetura TMR, há apenas uma etapa de troca de informação, onde cada microcontrolador envia aos outros dois, seu parecer referente à temperatura. Após isto, inicia-se a fase de votação. Já na arquitetura em anel, existem duas etapas de troca de informação. Na primeira, cada microcontrolador envia o seu parecer referente à temperatura, somente a um dos outros dois. Com base na comparação do parecer gerado com o recebido, cada MCU gera um código de erro. Segue então a segunda etapa de troca de informação, onde cada MCU envia seu código de erro as outras duas. Somente então, inicia-se a fase de votação.

Neste ponto, é importante lembrar, que nem todos os modelos de microcontroladores PIC possuem uma interface de comunicação serial, como possui o PIC 16F628. O PIC 16F84A, por exemplo, não a possui. Uma vez que, no início, ele foi o modelo utilizado para implementação das arquiteturas tolerantes a falhas descritas neste trabalho, foi necessária a implementação de rotinas para recepção e transmissão de dados. Essas rotinas foram aproveitadas para o PIC 16F628 e estão inseridas nas listagens dos programas. A rotina de recepção elaborada é capaz de reconhecer a falha de um módulo, quando este, depois de decorrido um tempo predeterminado, não transmite dados. Uma outra vantagem do emprego destas rotinas, é que a migração para modelos que não possuem USART pode ser realizada de maneira mais ágil e cômoda.

#### 3.3.6 Peculiaridades do software de cada módulo

Os programas implementados, para cada módulo de uma mesma arquitetura, embora similares, não são idênticos. A diferença fundamental, para ambas as arquiteturas, reside na tabela usada no processo de votação, para garantir que somente um microcontrolador exerça o controle, enquanto os demais aguardam.

A Tabela 3.5 mostra as linhas de comando para MCU  $\gamma$ . Esta MCU exerce o controle em duas situações distintas, a saber:

- 1- Quando o módulo posterior a ele (Módulo α) apresenta falha;

- 2- Sempre que os três módulos operam corretamente.

| Tabela 3.5 – Linhas de comando do software para MCU g. |             |                                         |

|--------------------------------------------------------|-------------|-----------------------------------------|

| MOVF                                                   | FLAGS,W     | ;COPIA VALOR DE FLAGS EM W              |

| ANDLW                                                  | B'00000111' | ;MASCARA VALOR, CONSIDERA SOMENTE ATÉ 7 |

| ADDWF                                                  | PCL,F       | ;PCL = (PCL+W)                          |

| GOTO                                                   | AGUARDA     | ;0                                      |

| GOTO                                                   | AGUARDA     | ;1                                      |

| GOTO                                                   | AGUARDA     | ;2                                      |

| GOTO                                                   | CONTROLA    | ;3                                      |

| GOTO                                                   | AGUARDA     | ;4                                      |

| GOTO                                                   | AGUARDA     | ;5                                      |

| GOTO                                                   | AGUARDA     | ;6                                      |

| GOTO                                                   | CONTROLA    | ;7                                      |

| Tabela 3.6 – Linhas de comando do software para MCU a e MCU b. |             |                                         |  |

|----------------------------------------------------------------|-------------|-----------------------------------------|--|

| MOVF                                                           | FLAGS,W     | ;COPIA VALOR DE FLAGS EM W              |  |

| ANDLW                                                          | B'00000111' | ;MASCARA VALOR, CONSIDERA SOMENTE ATÉ 7 |  |

| ADDWF                                                          | PCL,F       | ;PCL = (PCL+W)                          |  |

| GOTO                                                           | AGUARDA     | ;0                                      |  |

| GOTO                                                           | AGUARDA     | ;1                                      |  |