#### **PAPER**

## Performance of differential pair circuits designed with line tunnel FET devices at different temperatures

To cite this article: M D V Martino et al 2018 Semicond. Sci. Technol. 33 075012

View the article online for updates and enhancements.

#### Related content

- Analysis of current mirror circuits designed with line tunnel FET devices at different temperatures

M D V Martino, J A Martino, P G D Agopian et al.

- Performance of TFET and FinFET devices applied to current mirrors for different dimensions and temperatures

M D V Martino, J A Martino, P G D Agopian et al.

- Analog Parameters of Solid Source Zn Diffusion InXGa1XAs nTFETs down to 10 K C Bordallo, J A Martino, P G D Agopian et al.

### IOP ebooks™

Bringing you innovative digital publishing with leading voices to create your essential collection of books in STEM research.

Start exploring the collection - download the first chapter of every title for free.

Semicond. Sci. Technol. 33 (2018) 075012 (7pp)

https://doi.org/10.1088/1361-6641/aac4fd

# Performance of differential pair circuits designed with line tunnel FET devices at different temperatures

M D V Martino<sup>1,5</sup>, J A Martino<sup>1</sup>, P G D Agopian<sup>1,2</sup>, R Rooyackers<sup>3</sup>, E Simoen<sup>3</sup>, N Collaert<sup>3</sup> and C Claeys<sup>4</sup>

E-mail: mdvmartino@gmail.com

Received 24 January 2018, revised 23 April 2018 Accepted for publication 15 May 2018 Published 6 June 2018

#### **Abstract**

This work studies differential pair circuits designed with Line tunnel field effect transistors (TFETs), comparing their suitability with conventional Point TFETs. Differential voltage gain  $(A_d)$ , compliance voltage and sensitivity to channel length mismatch are analyzed experimentally for different temperatures. The first part highlights individual characteristics of Line TFETs, focusing on behaviors that affect analog circuits. In comparison to Point TFETs, Line TFETs present higher drive current, better transconductance and worse output conductance. In the second part, differential pairs are studied at room temperature for different dimensions and bias conditions. Line TFETs present the highest  $A_d$ , while Point TFET decrease the susceptibility to channel length mismatch. In the last part, the temperature impact is investigated. Based on the activation energy, the impact of band-to-band tunneling and trapassisted tunneling is discussed for different bias conditions. A general equation is proposed, including the technology and the susceptibility to temperature and dimensions. It was observed that Line TFETs are a good option to design differential pairs with higher  $A_d$  and ON-state current than Point TFETs.

Keywords: differential pair, analog performance, FinFET, Line TFET, Point TFET

(Some figures may appear in colour only in the online journal)

#### Introduction

At this point in time, where technological nodes reach the nanoscale domain, short channel effects, leakage currents and other undesirable behaviors become major roadblocks [1, 2]. Considering that the supply voltage and power dissipation cannot be scaled in the same ratio [3, 4], low power applications require new device concepts, such as tunnel field effect transistors (TFETs) [5, 6].

The basic TFET structure is a gate-controlled p-i-n diode, in which the dominant transport mechanism is band-to-band

tunneling (BTBT), instead of drift-diffusion. This way, it is theoretically possible to obtain a sub-60 mV/decade sub-threshold swing (SS) at room temperature [7–9]. On the other hand, measurements of point tunneling devices revealed that the magnitude of trap-assisted tunneling (TAT) in the OFF-state region may be a critical issue to reach the expected SS values [10, 11].

In this context, Line Tunnel FET structures have been proposed in order to avoid SS degradation and to enhance the drive current [12, 13]. These devices are characterized by a source/gate overlap, so that the direction of tunneling and the gate electric field become aligned [14, 15]. While the Point TFETs ON-state current is unaffected by the channel length,

<sup>&</sup>lt;sup>1</sup>LSI/PSI/USP, University of Sao Paulo, Sao Paulo, Brazil

<sup>&</sup>lt;sup>2</sup> Sao Paulo State University (UNESP), Campus Sao Joao da Boa Vista, Brazil

<sup>&</sup>lt;sup>3</sup> Imec, Leuven, Belgium

<sup>&</sup>lt;sup>4</sup>E.E. Department, KU Leuven, Leuven, Belgium

<sup>&</sup>lt;sup>5</sup> Author to whom any correspondence should be addressed.

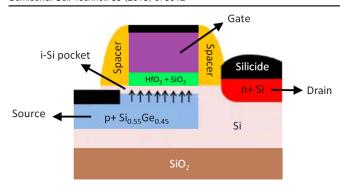

Figure 1. Line Tunnel FET structure.

this design proposed for Line TFETs makes its current to vary proportionally not only to the channel width but also to the channel length [16, 17].

Due to the promising advantages of individual TFETs, basic circuits have also been analyzed in recent papers [18, 19]. For instance, digital configurations such as multiplexers and inverters have been studied, mainly by simulations [20, 21], with a couple of papers presenting experimental data as well [22, 23]. Simulation approaches have also been used to investigate some basic analog applications [24–27].

Bearing interesting digital and analog applications in mind, this paper presents the experimental performance of Line Tunnel FET devices in a widely used circuit, namely a differential pair. The results are analyzed for different dimensions, bias conditions and temperatures. Preliminary results at room temperature have been published in [28] and other structures, such as Point TFETs, have been studied in [29, 30]. This way, it was possible to compare the results for these different technologies, with conclusions on the suitability of each of them in differential pair circuits.

#### **Device characteristics**

The experimental results mentioned in this paper refer to transistors fabricated on 300 mm silicon-on-insulator wafers at imec/Belgium. The devices present a Si/SiGe heterojunction, known to provide enhanced performance, due to the lower bandgap at the source [31]. Line-nTFETs have been used, with a thin intrinsic silicon pocket layer on top of a p-type Si<sub>0.55</sub>Ge<sub>0.45</sub> source, which extends under the gate. Source and drain regions are separated by an undoped Si channel.

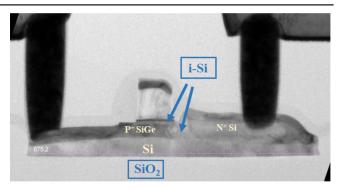

The gate stack is composed of interfacial  $SiO_2$  (1 nm),  $HfO_2$  (1.8 nm) and TiN (2 nm), followed by deposition of p-doped amorphous silicon. In terms of channel mask dimensions, selected devices present a width of 70, 100 and 130 nm, and a length of 70 and 130 nm, respectively. Figure 1 shows a schematic structure of a Line Tunnel FET device while figure 2 gives a TEM image of a processed device. More details can be found in [31].

The Line TFET working principle is based on an increasing gate bias resulting in a potential well in the pocket conduction band. When the lowest sub-band in the pocket conduction band aligns with the source valence band, tunneling is triggered. Then, the positively biased drain collects the electrons, leading to a current with its magnitude increasing for wider and longer

Figure 2. TEM image of a Line Tunnel FET structure.

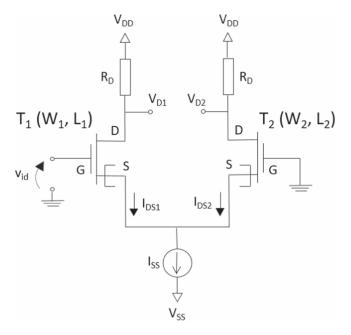

Figure 3. Differential pair circuit.

channels. This channel length dependence is different from the inverse proportionality observed for e.g. FinFETs and the non-dependence obtained for Point TFETs [5, 16, 17].

#### Methodology

The differential pair circuit is represented in figure 3. A differential input voltage  $(v_{id})$  is applied on the  $T_1$  gate, while the  $T_2$  gate is grounded. The output  $V_{D1}$  is used to determine the differential voltage gain  $(A_d)$ , defined as the ratio  $A_d = |V_{D1}|/|\Delta v_{id}|$ .

The analyses have been performed for different bias conditions, with  $1.3~{\rm V} \leqslant |V_{\rm SS}| \leqslant 1.5~{\rm V}$  and  $-0.4~{\rm V} \leqslant v_{\rm id} \leqslant +0.4~{\rm V}$ .  $V_{\rm DD}$  has been connected to ground. The susceptibility of the circuit to the transistors dimensions has been explored as well, with different values of channel width (70, 100 and 150 nm) and length (70 and 130 nm). Measurements have been taken for temperatures ranging from 25 °C to 175 °C.

#### Results and analysis

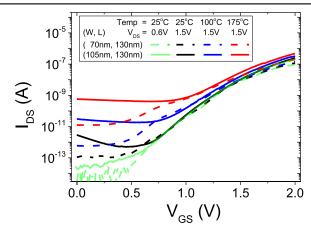

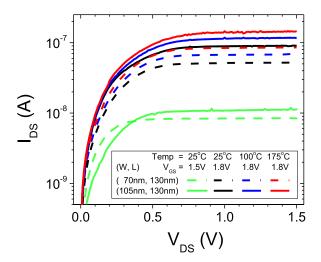

First of all, individual characterizations have been performed for each Line TFET at room and high temperatures. Figures 4

**Figure 4.** Drain current as a function of  $V_{\rm GS}$  for Line TFETs with different dimensions,  $V_{\rm DS}$  values and temperatures.

**Figure 5.** Drain current as a function of  $V_{\rm DS}$  for Line TFETs with different dimensions,  $V_{\rm GS}$  values and temperatures.

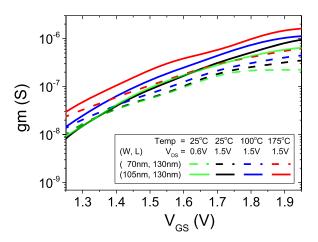

**Figure 6.** Transconductance as a function of  $V_{\rm GS}$  for Line TFETs with different dimensions,  $V_{\rm DS}$  values and temperatures.

and 5 show the input and output characteristic curves, respectively, revealing the impact of devices dimensions, bias condition and temperature. Meanwhile, figure 6 exhibits the transconductance as a function of the gate voltage and

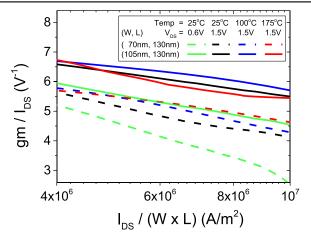

Figure 7. Transistor efficiency as a function of normalized drain current for Line TFETs with different dimensions,  $V_{\rm DS}$  values and temperatures.

figure 7 illustrates the transistor efficiency as a function of the normalized drain current. Both of them are represented for the same bias and temperature conditions as figure 4, highlighting the on-state region.

Based on the previously explained Line TFET working principle, it is known that both  $I_{\rm DS}$  and gm are directly proportional to the channel area. This is the reason for the normalization method applied for the plots in figure 7. A different channel length dependence is expected for FinFETs, in which the current decreases for longer channels due to the drift/diffusion mechanism, and for Point TFETs, which are not susceptible to the channel length due to the local tunneling perpendicular to the gate electric field.

This channel length dependence is summed up by equation (1), published and explained in [32]. The introduced parameter m refers to the different drain current susceptibility to the effective values of channel length ( $L_{\rm ef}$ ), leading to different behaviors of differential pairs designed with each technology.

$$I_{\rm DS} \propto \frac{W_{\rm ef}}{L_{\rm ef}^{m}},$$

(1)

where:  $m_{\text{Line TFET}} = -1$ ;  $m_{\text{Point TFET}} = 0$ .

It is worth mentioning that analogous input and output characteristic curves for Point TFET devices are reported in [33, 34]. Therefore, it is possible to compare relevant parameters, such as  $I_{DS}$ , gm,  $g_D$  and  $r_0$ . For instance, a Line TFET presents much higher on-state current when compared to a Point TFET, with an expected difference of up to 3 orders of magnitude for similar bias condition and channel dimensions. In terms of transconductance, the order of magnitude observed for Line TFETs in figure 6 (gm  $\sim 10^{-7}$  S) is better than the lower values obtained for Point TFETs. On the other hand, regarding the output conductance and resistance, Line TFETs typical values can be extracted from figure 5  $(g_{\rm D} \sim 10^{-9} \, {\rm S}, \, r_0 \sim 10^9 \, \Omega)$ , which are worse than the ones observed for Point TFETs. Such parameters will also lead to differences in the behavior of basic circuits built with each of these technologies. This way, this individual comparison will be recapped in order to justify the differences observed in

**Figure 8.** Normalized drain current as a function of differential input voltage for Line TFETs with different bias conditions values.

relevant differential pairs parameters, such as the differential voltage gain (table 1).

#### Analysis of differential pairs at room temperature

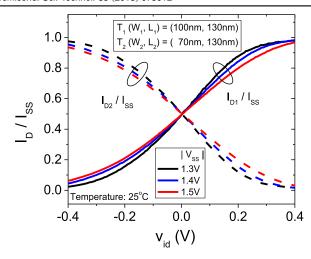

After the analyses of individual devices, three differential pair circuits have been measured for different bias conditions. Figure 8 shows the normalized drain currents,  $I_{\rm D1}/I_{\rm SS}$  and  $I_{\rm D2}/I_{\rm SS}$ , as a function of  $v_{\rm id}$ . It is possible to notice an increase in the overdrive voltage for higher values of  $I_{\rm SS}$  (and  $V_{\rm SS}$ ), due to the raise in the gate-source voltage. This leads to a wider linear region, and a resulting higher compliance voltage, similarly to the trend observed for Point TFETs. The compliance voltage for Line TFETs and Point TFETs are close to each other [29]. The slope observed in figure 8 and the absolute values of drain current, showed in figure 4, can be used to extract the differential voltage gain for each condition. This way, since higher values of  $V_{\rm SS}$  cause a significant increase in  $I_{\rm SS}$  and a slight decrease in the normalized current slope, the overall value of  $A_{\rm d}$  increases with  $V_{\rm SS}$ .

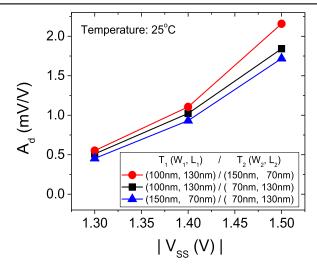

Figure 9 sums up the bias impact on three different configurations of basic pair circuits. There is a similar trend of  $A_{\rm d}$  susceptibility to  $V_{\rm SS}$ , but the absolute values are higher for circuits designed with transistors with larger channel areas. Even with similar normalized current slopes, the difference once more follows the expected increase with  $I_{DS}$  for transistors with larger channel areas. This way, a similar procedure could lead to a comparison of  $A_d$  for Line TFETs and Point TFETs. In a general equation, the differential voltage gain may be expressed by two components: one represents the base magnitude value from the technology and bias condition (fitting parameter p), while the other comes from the drain current susceptibility to the channel dimensions (equation (1)).

$$A_{\rm d} = p({\rm technology, bias}) \times f\left(\frac{W_{\rm ef1}}{L_{\rm ef1}^m}, \frac{W_{\rm ef2}}{L_{\rm ef2}^m}\right),$$

(2)

where:  $m_{\text{Line TFET}} = -1$ ;  $m_{\text{Point TFET}} = 0$ .

**Figure 9.** Differential voltage gain as a function of  $V_{\rm ss}$  for Line TFET pairs with different dimensions.

**Figure 10.** Activation energy as a function of  $V_{\rm GS}$  for Line TFETs with different values of channel length and width.

**Table 1.** Features presented by differential pairs designed with Point TFET and Line TFET devices.

|                                               | Point TFET | Line TFET |

|-----------------------------------------------|------------|-----------|

| High differential voltage gain                |            | <b>√</b>  |

| High on-state current                         |            | ✓         |

| Low susceptibility to channel length mismatch | ✓          |           |

| Low susceptibility to the temperature         | ✓          | ✓         |

#### Analysis of differential pairs at high temperature

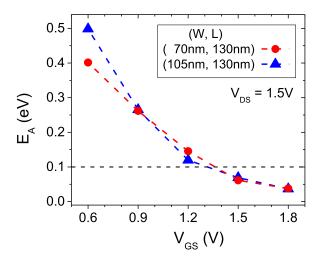

The analysis of differential pair circuits at room temperature has been followed by the study of temperature impact, making use of previously obtained individual characteristics and including the activation energy in order to investigate the prevailing transport mechanism for different bias conditions. The activation energy values for the same devices represented in figures 4–6 are exhibited in figure 10.

**Figure 11.** Normalized drain current as a function of differential input voltage for Line TFETs at different temperatures.

When the activation energy gets lower than 0.1 eV, the prevailing mechanism is BTBT, while TAT dominates otherwise [35]. This means that, when  $|I_{\rm SS}|$  is set so that  $|V_{\rm SS}|=1.5~{\rm V}$  for  $v_{\rm id}=0~{\rm V}$ , and then  $v_{\rm id}$  ranges from  $-0.4~{\rm to}$  +0.4 V, there will be a transition in the prevailing transport mechanism.

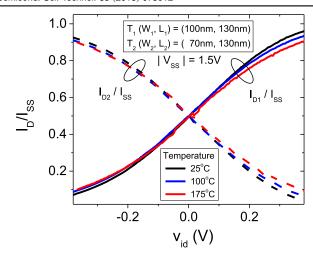

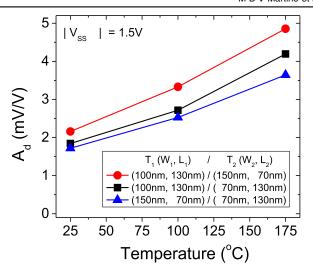

Figure 11 shows the normalized drain currents as a function of  $v_{id}$  for the same pair studied in figure 8, but now including data for three different temperatures. It is possible to notice a slight decrease in the slope for higher temperatures. On the other hand, since this difference is much smaller than the increase in  $I_{SS}$  observed (figure 4) for 100 °C and 175 °C, the overall differential voltage gain increases with temperature. This global impact of the temperature on  $A_d$  is illustrated in figure 12, including the same pairs previously studied at room temperature (figure 9).

Considering that the differential voltage gain is calculated based on the slope for  $v_{\rm id}=0\,{\rm V}$  and  $|V_{\rm SS}|=1.5\,{\rm V}$ , it is important to remember that it refers to the condition for which  ${\rm T}_1$  and  ${\rm T}_2$  are dominated by BTBT. Therefore, the  $A_{\rm d}$  dependence on the temperature basically comes from the band gap  $(E_{\rm g})$  narrowing for higher temperatures, mathematically shown in equation (3) [36]. For the temperature range discussed in this work, there is a roughly linear dependence.

$$I_{\rm BTBT} \propto e^{(-k.E_g^{3/2})}. \tag{3}$$

It is interesting to remember that the positive trend of  $A_{\rm d}$  with temperature observed in figure 12, as a consequence of tunneling enhancement, is a very relevant difference when compared to conventional MOS devices, in which the negative trend is due to mobility degradation (and decreasing gm) under higher temperatures. For instance, a previous comparative study [30] showed a steep decrease by more than 50% in  $A_{\rm d}$  for a differential pair with FinFETs exposed to the same temperature variation studied in this paper, in a way that the lower susceptibility to the temperature may be considered a very relevant advantage of TFET devices.

Therefore, a fitting parameter q, dependent on the activation energy of  $T_1$  and  $T_2$  impact at the operation

**Figure 12.** Differential voltage gain as a function of temperature for Line TFET pairs with different dimensions.

temperature, could be included in equation (2). In this way, the general equation (4) takes into consideration also the temperature impact and its consequent dominant transport mechanism.

$$A_{\rm d} = p({\rm technology, bias}) \times q(E_{A1}, E_{A2}) \times f\left(\frac{W_{\rm ef1}}{L_{\rm ef1}^m}, \frac{W_{\rm ef2}}{L_{\rm ef2}^m}\right),$$

$$(4)$$

where:  $m_{\text{Line TFET}} = -1$ ;  $m_{\text{Point TFET}} = 0$ .

Finally, it is possible to make a comparison of differential pairs designed with different technologies in terms of differential voltage gain, on-state current, susceptibility to channel length mismatch and susceptibility to the temperature.

It is worth remembering that differential voltage gain  $(A_{\rm d})$  of a differential pair is directly proportional to its differential pair transistor transconductance (gm) and to the output resistance  $(R_{\rm O})$  resulting from the parallel association of output transistor resistance  $r_0$  and load resistance  $R_{\rm D}$   $(R_{\rm O}=r_0//R_{\rm D})$ . The individual parameters analysis based on figures 4–7 (Line TFETs) and on [33, 34] (Point TFETs) can be used to compare the resulting differential voltage gain for each technology. Since typical values of  $r_0$  are much higher than  $R_{\rm D}$ , the difference in  $A_{\rm d}$  will derive basically from the contrast in gm. In other words, for differential pairs designed with the same external resistance, Line TFET higher values of gm always lead to a circuit with higher differential voltage gain.

Meanwhile, differential pairs designed with Line TFETs tend to present higher on-state currents, but Point TFETs are important for applications in which channel length mismatch is an issue. Both Point TFET and Line TFET can take advantage of the lower temperature dependence of BTBT and provide a less susceptible circuit in this point of view. Table 1 summarizes the features of each technology in terms of important parameters for differential pairs.

Therefore, Line TFET technology is a very good option for applications requiring high differential voltage gain and low susceptibility to temperature variation, since it can take advantage of a relatively high on-state current, which is a known disadvantage of Point TFET devices, and the suitable transport mechanism, typical of tunneling devices.

#### **Conclusions**

This work studied the performance of differential pairs designed with Line TFETs, based on experimental data obtained at room and high temperature. The suitability of this technology in comparison to Point TFET was discussed, including besides temperature, also dimensions and bias influence.

Line TFETs present the best values of drive current and gm, while Point TFET are the most suitable in term of  $g_D$ . These behaviors impact the differential pair designed with each kind of device. Combining the normalized current slope with the drive current magnitude, it was extracted that Line TFETs yield the highest differential voltage gain.

The analysis of the temperature impact points out that there was a transition in the dominant transport mechanism for the input differential voltage range, varying from TAT to BTBT. In order to extract the differential voltage gain as a function of temperature, both transistors in the differential pair have been biased such that BTBT was the prevailing mechanism. Since this mechanism causes a slight increase in the on-state current for higher temperatures, the effect on the circuit was an increase in the differential voltage gain for higher temperatures, in contrast to the  $A_{\rm d}$  degradation observed for conventional MOS circuits. A global generic equation for the differential voltage gain as a function of technology, devices dimensions and temperature parameters has been proposed.

Taking all the results into consideration, it was possible to sum up the advantages and disadvantages of designing differential pair circuits with each of the studied technologies. If low susceptibility to channel length mismatch is a strong requirement, Point TFET would be the best option, but if the application requires a higher differential voltage gain, Line TFET devices would lead to the best overall performance. Therefore, it was possible to experimentally investigate Line TFET technology application in differential pairs at room and high temperature.

#### **Acknowledgments**

The authors would like to thank CNPq and FAPESP for the financial support during the execution of this work. Part of the work was supported by the imec's Logic Device Program and its core partners.

#### **ORCID iDs**

M D V Martino https://orcid.org/0000-0003-2018-5092 P G D Agopian https://orcid.org/0000-0002-0886-7798

#### References

- [1] Reddick W M and Amaratunga G A J 1995 Silicon surface tunnel transistor *Appl. Phys. Lett.* **67** 494–6

- [2] Krishnamohan T, Kim D, Raghunathan S and Saraswat K 2008 Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and ≪60 mV/dec subthreshold slope *IEEE Int. Electron Devices Meeting* pp 1–3

- [3] Nikonov D E and Young I A 2012 Uniform methodology for benchmarking beyond-CMOS logic devices *IEEE IEDM* pp 573–6

- [4] Tomioka K, Yoshimura M and Fukui T 2012 Steep-slope tunnel field-effect transistors using III–V nanowire/Si heterojunction Symp. on VLSI Technology (VLSIT) pp 47–8

- [5] Wu J, Min J and Taur Y 2015 Short-channel effects in tunnel FETs IEEE Trans. Electron Devices 62 3019–24

- [6] Liu L, Mohata D and Datta S 2012 Scaling length theory of double-gate interband tunnel field-effect transistors *IEEE Trans. Electron Devices* 59 902–8

- [7] Mookerjea S, Krishnan R, Datta S and Narayanan V 2009 Effective capacitance and drive current for tunnel FET (TFET) CV/I estimation *IEEE Trans. Electron Devices* 56 2092–8

- [8] Wu J and Taur Y 2016 A continuous semianalytic current model for DG and NW TFETs IEEE Trans. Electron Devices 63 841–7

- [9] Der Agopian P G, Martino J A, Rooyackers R, Vandooren A, Simoen E and Claeys C 2013 Experimental comparison between Trigate p-TFET and p-FinFET analog performance as a function of temperature *IEEE Trans. Electron Devices* 60 2493–7

- [10] Zhao Q T et al 2012 Tunneling field-effect transistor with a strained Si channel and a Si<sub>0.5</sub>Ge<sub>0.5</sub> source Solid-State Electron. 74 97–101

- [11] Nayfeh O M 2011 Heterojunction tunneling transistors using gate-controlled tunneling across silicon–germanium/silicon epitaxial thin films IEEE Electron Device Lett. 32 844–6

- [12] Leonelli D, Vandooren A, Rooyackers R, Verhulst A, Huyghebaert C, De Gendt S, Heyns M and Groeseneken G 2011 Novel architecture to boost the vertical tunneling in tunnel field effect transistors *IEEE Int. SOI Conf.* pp 1–2

- [13] Zhou G *et al* 2012 Novel gate-recessed vertical InAs/GaSb TFETs with record high ION of 180  $\mu$ A  $\mu$ m<sup>-1</sup> at  $V_{\rm DS}=0.5$  V *Int. Electron Devices Meeting* pp 1–32

- [14] Chang H Y, Adams B, Chien P Y, Li J and Woo J C S 2013 Improved subthreshold and output characteristics of sourcepocket Si tunnel FET by the application of laser annealing IEEE Trans. Electron Devices 60 92-6

- [15] Moselund K E, Schmid H, Bessire C, Bjork M T, Ghoneim H and Riel H 2012 InAs–Si nanowire heterojunction tunnel FETs IEEE Electron Device Lett. 33 1453–5

- [16] Martino M D V, Martino J A and Agopian P G D 2014 Drain induced barrier thinning on TFETs with different source/ drain engineering 29th Symp. on Microelectronics Technology and Devices (SBMicro) pp 1–4

- [17] Mohata D K *et al* 2012 Demonstration of improved heteroepitaxy, scaled gate stack and reduced interface states enabling heterojunction tunnel FETs with high drive current and high on–off ratio *Symp. on VLSI Technology (VLSIT)* pp 53–4

- [18] Huang Q, Huang R, Wu C, Zhu H, Chen C, Wang J, Guo L, Wang R, Ye L and Wang Y 2014 Comprehensive performance re-assessment of TFETs with a novel design by gate and source engineering from device/circuit perspective Technical Digest—Int. Electron Devices Meeting, IEDM pp 1-13

- [19] Alioto M and Esseni D 2014 Performance and impact of process variations in Tunnel-FET ultra-low voltage digital circuits Proc. 27th Symp. on Integrated Circuits and Systems Design (SBCCI '14) pp 1–6

- [20] Morris D H, Avci U E, Rios R and Young I A 2014 Design of low voltage tunneling-FET logic circuits considering asymmetric conduction characteristics *IEEE J. Emerg. Sel. Top. Circuits Syst.* 4 380–8

- [21] Shaik S, Krishna K and Vaddi R 2016 Circuit and architectural co-design for reliable adder cells with steep slope tunnel transistors for energy efficient computing *Proc. Int. Conf. on* VLSI Design pp 306–11

- [22] Richter S, Schulte-Braucks C, Knoll L, Luong G V, Schäfer A, Trellenkamp S, Zhao Q T and Mantl S 2014 Experimental demonstration of inverter and NAND operation in p-TFET logic at ultra-low supply voltages down to  $V_{\rm DD}=0.15~{\rm V}$  72nd Device Research Conf. pp 23–4

- [23] Avci U E, Hasan S, Nikonov D E, Rios R, Kuhn K and Young I A 2012 Understanding the feasibility of scaled III– V TFET for logic by bridging atomistic simulations and experimental results *Symp. on VLSI Technology (VLSIT)* pp 183–4

- [24] Sedighi B, Hu X S, Liu H, Nahas J J and Niemier M 2015 Analog circuit design using tunnel-FETs IEEE Trans. Circuits Syst. 1: Regular Papers 62 39–48

- [25] Kaushal G, Subramanyam K, Rao S N, Vidya G, Ramya R, Shaik S, Jeong H, Jung S O and Vaddi R 2014 Design and performance benchmarking of steep-slope tunnel transistors for low voltage digital and analog circuits enabling selfpowered SOCs Int. SoC Design Conf. (ISOCC) pp 32–3

- [26] Biswas A, Luong G V, Chowdhury M F, Alper C, Zhao Q T, Udrea F, Mantl S and Ionescu A M 2017 Benchmarking of homojunction strained-Si NW tunnel FETs for basic analog functions *IEEE Trans. Electron Devices* 64 1441–8

- [27] Settino F, Lanuzza M, Strangio S, Crupi F, Palestri P, Esseni D and Selmi L 2017 Understanding the potential and limitations of tunnel FETs for low-voltage analog/mixedsignal circuits *IEEE Trans. Electron Devices* 64 2736–43

- [28] Martino M D V, Martino J A, Agopian P G D, Rooyackers R, Simoen E, Collaert N and Claeys C 2017 Experimental analysis of differential pairs designed with line tunnel FET devices IEEE SOI-3D-Substhreshold Microelectronics Technology Unified Conf. (S3S)

- [29] Martino M D V, Martino J A and Agopian P G D 2015 Performance comparison between TFET and FinFET differential pair 30th Symp. on Microelectronics Technology and Devices (SBMicro) pp 1–4

- [30] Martino M D V, Martino J A and Agopian P G D 2016 Analysis of TFET and FinFET differential pairs with active load from 300 K to 450 K Joint Int. EUROSOI Workshop and Int. Conf. on Ultimate Integration on Silicon (EUROSOI-ULIS) pp 246–9

- [31] Walke A M *et al* 2014 Fabrication and analysis of a Si/Si<sub>0.55</sub>Ge<sub>0.45</sub> heterojunction line tunnel FET *IEEE Trans. Electron Devices* **61** 707–15

- [32] Martino M D V, Martino J A, Agopian P G D, Vandooren A, Rooyackers R, Simoen E and Claeys C 2017 Analysis of current mirror circuits designed with line tunnel FET devices at different temperatures Semicond. Sci. Technol. 32 055015

- [33] Martino M D V, Martino J A, Agopian P G D, Vandooren A, Rooyackers R, Simoen E, Thean A and Claeys C 2016 Performance of TFET and FinFET devices applied to current mirrors for different dimensions and temperatures Semicond. Sci. Technol. 31 055001

- [34] Martino M D V, Martino J A, Agopian P G D, Vandooren A, Rooyackers R, Simoen E, Thean A and Claeys C 2015 Comparison of current mirrors designed with TFET or FinFET devices for different dimensions and temperatures ECS Trans. 66 303–8

- [35] Vandooren A, Leonelli D, Rooyackers R, Hikavyy A, Devriendt K, Demand M, Loo R, Groeseneken G and Huyghebaert C 2013 Analysis of trap-assisted tunneling in vertical Si homo-junction and SiGe hetero-junction Tunnel-FETs Solid-State Electron. 83 50–5

- [36] Schenk A 1993 Rigorous theory and simplified model of the bandto-band tunneling in silicon Solid-State Electron. 36 19–34