ELSEVIER

Contents lists available at ScienceDirect

## Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Study of line-TFET analog performance comparing with other TFET and MOSFET architectures

Paula Ghedini Der Agopian <sup>a,b,\*</sup>, João Antonio Martino <sup>a</sup>, Anne Vandooren <sup>c</sup>, Rita Rooyackers <sup>c</sup>, Eddy Simoen <sup>c</sup>, Aaron Thean <sup>c</sup>, Cor Claeys <sup>c,d</sup>

- <sup>a</sup> LSI/PSI/USP University of São Paulo, Av. Prof. Luciano Gualberto, trav. 3 nº 158, 05508-010 Sao Paulo, Brazil

- <sup>b</sup> UNESP Universidade Estadual Paulista, São João da Boa Vista, Brazil

- c imec, Kapeldreef 75, B-3001 Leuven, Belgium

- <sup>d</sup> E.E. Dept, KULeuven, Leuven, Belgium

#### ARTICLE INFO

Article history:

Available online 15 October 2016

The review of this paper was arranged by Viktor Sverdlov

Keywords: Line-TFET Intrinsic voltage gain Different device architectures

#### ABSTRACT

In this work the Line-TFET performance is compared with MOSFET and Point-TFET devices, with different architectures (FinFET and GAA:Gate-All-Around) at both room and high temperatures. This analysis is based on the experimental basic analog parameters such as transconductance (gm), output conductance (gD) and intrinsic voltage gain (AV). Although the Line-TFETs present worse AV than the point-TFETs, when they are compared with MOSFET technology, the line-TFET shows a much better intrinsic voltage gain than both MOSFET architectures (FinFET and GAA). Besides the AV, the highest on-state current was obtained for Line-TFETs when compared with other two TFET architectures, which leads to a good compromise for analog application.

© 2016 Elsevier Ltd. All rights reserved.

#### 1. Introduction

Tunnel-FETs have been proposed by the international community as an alternative for MOSFETs, when focusing on extremely small technology nodes, due to their high speed switching capability [1] that allows to improve the energy efficiency of switches. However, as the low on-current is a problem of homo-junction TFETs, several works report research on different materials and different geometries aiming to reach a smaller subthreshold swing and an on-current improvement [2,3].

A planar Line-TFET is an alternative structure that increases the electric field at the source-pocket junction and consequently improves the on-current and reduces the subthreshold swing when compared with the point-TFET silicon devices [4–6].

Although the main focus of the tunnel-FET is the digital switch, some recent work has also pointed out the great potential of these devices for analog applications [7-10].

In this work the planar heterojunction Line-nTFET is experimentally analyzed through the basic analog parameters, focusing mainly on intrinsic voltage gain. A comparison of the intrinsic voltage gain of Line-TFETs with devices with different architectures

E-mail address: agopian@lsi.usp.br (P.G.D. Agopian).

like FinFET (MOSFET and TFETs) [7] and Gate-all-around (MOSFET and TFET) [11] is also performed, for temperatures ranging from room up to 150 °C. For vertical GAA-TFETs, different source compositions (Si and  $Si_{0.73}Ge_{0.27}$ ) will be also considered.

#### 2. Device characteristics

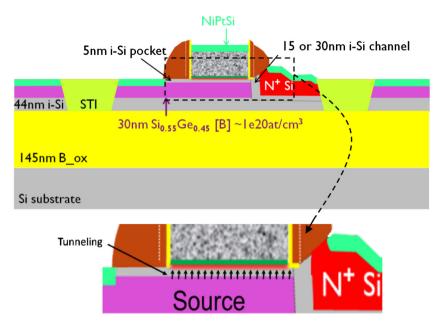

The studied Line-nTFETs are Si/SiGe heterojunction devices fabricated on silicon-on-insulator wafers at imec/Belgium. The p-type  $Si_{0.55}Ge_{0.45}$  source extends under the gate and a thin intrinsic silicon pocket layer ( $\sim$ 5 nm) is on top. The source and the drain regions are separated by a nominally undoped Si channel.

The gate stack is composed by a 1 nm interfacial  $SiO_2$  layer followed by 1.8 nm of HfO<sub>2</sub>, 2 nm of TiN and p-doped amorphous sillon. The channel width (W) ranges from 110 nm to 200 nm and two different gate lengths (L) (1  $\mu$ m and 130 nm) were evaluated.

Fig. 1 presents a schematic structure of a Line-TFET and more details on this structure/fabrication can be found in [6].

#### 3. Analysis and discussion

Since the source of Line-TFETs extends under the gate region, this architecture promotes tunneling in the same electric field direction, which is more efficient than the conventional point-tunneling. Besides, the position of the tunneling source/channel

<sup>\*</sup> Corresponding author at: LSI/PSI/USP – University of São Paulo, Av. Prof. Luciano Gualberto, trav. 3  $\rm n^o$  158, 05508-010 Sao Paulo, Brazil.

Fig. 1. Line-TFET structure.

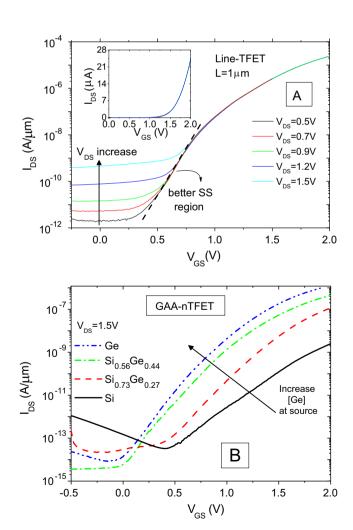

**Fig. 2.** Experimental normalized transfer curves of a Line-TFET for different drain bias (A) and of a point-TFET for different source compositions [12] (B).

junction makes the total tunneling proportional to the  $L \times W$  dimensions.

Fig. 2 presents the transfer characteristic normalized by the channel width of a single Line-TFET for different drain bias (A) and for point-TFETs with different source composition (B) as a function of gate voltage. From Fig. 2, it is possible to observe that Line-TFETs (2A) reaches a higher on-state current than point-TFETs (2B), considering the same channel width. This ON-current improvement, promoted by the Line-TFET structure, is a result of the alignment of the electric field with the tunneling direction that in turns, results in a strong energy band bending, increasing the band-to-band current. It is also possible to observe from the Line-TFET transfer characteristics (Fig. 2A) that the smaller the drain bias ( $V_{\rm DS}$ ), the steeper the drain current ( $I_{\rm DS}$ ) in the subthreshold region due to the off current reduction. The SS improvement becomes even more pronounced with increasing gate length and consequently the tunneling area as reported in [6].

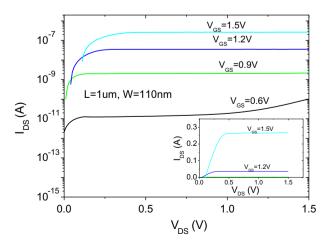

Besides the high on state current, when the output characteristic is evaluated (Fig. 3), the line-TFET also presents a good plateau in the saturation like region, showing to be a promising device for

Fig. 3. Experimental output characteristic of a Line-TFET for different gate bias.

analog applications, as was already reported for point-TFETS [7,8]. However, at low gate bias, it is clear that the saturation like region does not present a plateau, i.e., the output characteristic is degraded and becomes inappropriate for this kind of application. Since the drain current level changes several orders of magnitude with the gate bias increase, the drain current was also plotted in a linear scale (inset), in order to better observe the plateau region, confirming the aforementioned.

Considering that the intrinsic voltage gain  $(A_V)$  is one of the most important figures of merit for analog applications and it can be calculated by the transconductance (gm) over output conductance  $(g_D)$  ratio, these parameters were evaluated for different bias, channel lengths and channel widths, aiming to optimize the Line-TFET  $A_V$  performance.

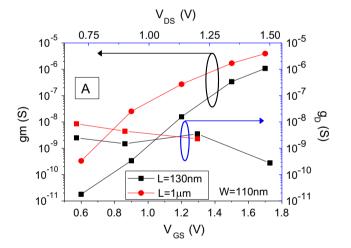

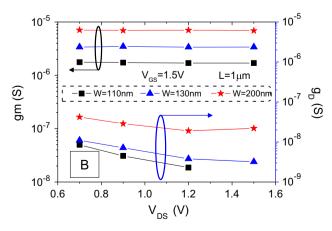

The gm and  $g_D$  analysis were performed for different channel lengths and different channel widths in order to select the best combination of the transistor dimensions to optimize the  $A_V$  value as can be seen in Fig. 4.

From Fig. 4A, it is possible to notice that although gm increases with the gate bias due to the higher overlap between bands, similarly as occurs for point-TFETs, when the comparison between line and point TFETs focus on the gm dependence with channel length, the line-TFETs presents a direct dependence on L, while point devices usually are independent on it. The higher gm for longer channel length occurs due to the larger tunneling junction area underneath the gate as shown in Fig. 4 (source/Si pocket).

**Fig. 4.** Transconductance (Left/Bottom axis) and output conductance (Right/Top axis) for different channel lengths (A) and for different channel widths as a function of  $V_{DS}$  (B).

However, evaluating the  $g_D$  values, a smaller gate length dependence is observed. Besides this, as  $V_{DS}$  increases, the TFET devices operate more in the "saturation like" region, resulting in a better (smaller)  $g_D$ .

The dependence of these two parameters ( $g_D$  and gm) on channel width (W) were also evaluated for high  $V_{GS}$  (1.5 V) as a function of drain bias (Fig. 4B). Although the drain bias does almost not affect the transconductance, it increases with the channel width, as expected, due to the junction area increase. Focusing on output conductance ( $g_D$ ), it was observed that it depends on both the drain bias and the channel width, but in the opposite way. While the higher drain bias contributes to the  $g_D$  improvement (the TFET operates more in the "saturation like" region), the drain current increases with channel width resulting in a  $g_D$  degradation (increase).

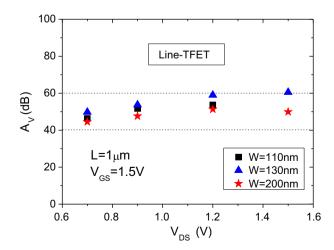

Keeping in mind that the transconductance presented a significant improvement for longer channel device, while the variation on output conductance is not so important, the obtained intrinsic voltage gain ( $A_V$ ) for longer devices was higher than the shorter one. Fig. 5 shows the experimental  $A_V$  for long line-TFETs ( $L=1~\mu m$ ) with different channel widths operating at different drain bias. From Fig. 5 it is possible to observe that the output characteristic improvement associated with a  $V_{DS}$  increase leads to an optimization of the bias operation point for the analog performance of all Line-TFETs. However, when the channel width (W) was evaluated, the response of a transistor with W of 130 nm, shows a reduction of two times on transconductance and a strong reduction on  $g_D$  compared with their counterpart with W=200~nm, that in turns, results in a best  $A_V$  value for devices with W=130~nm and  $L=1~\mu m$ .

Since the line-TFET with W=130~nm and  $L=1~\mu\text{m}$  shows to be slightly better and the best bias condition was defined above for the line-TFET architecture and it was already performed for TFET-FinFET and GAA-FinFET architectures in [7,8], respectively, from now on, their analog performance is compared among these three different architectures. Besides this analysis, a comparison of this planar Line-TFET was also performed for different technologies (MOS and TFET).

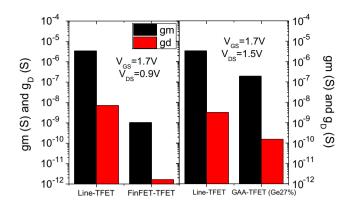

The first comparison, shown in Fig. 6, is focused on gm and  $g_D$  of these three different architectures. Comparing the TFETs fabricated in a planar (line) and FinFET structure (Fig. 6A) it is possible to see that both transconductance and output conductance obtained for planar devices are very high because the line TFETs becomes to be dominated by the earlier start of the Band-to-band tunneling phenomena. However, considering the vertical GAA structure

Fig. 5. Experimental  $A_V$  for Line-TFETs for different  $V_{DS}$  and channel widths at  $V_{GS}$  = 1.5 V.

**Fig. 6.** Experimental comparison of gm and  $g_D$  at optimum point for different architectures: Line-TFET  $\times$  FinFET (A) and Line-TFET  $\times$  GAA-TFET (B).

(Fig. 6B), only the transconductance stands out due to its improvement.

Making the analog evaluation for different temperatures (from room to 150 °C), the  $A_V$  performance among the planar Line-TFET and transistors fabricated with the FinFET structure (tunnel-FET and MOSFET), shows a smaller  $A_V$  for Line-TFETs than for the TFET with the FinFET structure (Fig. 7). It occurs because line-TFETs are more dependent of BTBT and as a consequence a higher  $g_D$  was obtained.

However, when line-TFETs are compared with the conventional FinFETs (MOSFET technology), the  $A_V$  of Line-TFETs is at least 30 dB higher for all temperatures because the BTBT tunneling current is less dependent of  $V_{DS}$  than the drift current.

Considering the gate-all around transistors, like nanowire devices, it is well known that for smaller diameter, the coupling between gate and channel is higher, resulting in a predominance of BTBT rate along all the source/channel junction area [13]. As a consequence it can be obtained a better subthreshold swing behavior, higher gm and consequently higher transistor efficiency (gm/  $I_{DS}$ ) at weak conduction regime as reported by [14], which increases the intrinsic voltage gain increases only in this operation region. However, transistors with higher diameter is more TAT dependent (less BTBT dependence), which degrades the weak inversion, but it is less drain voltage dependent, resulting in a better output conductance, Early voltage and consequently the intrinsic voltage gain at strong conduction as already reported in [7,8].

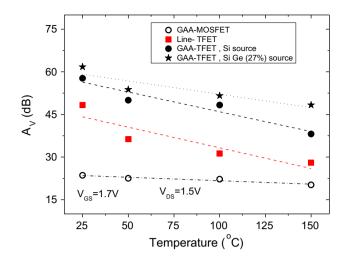

Focusing on the performance of intrinsic voltage gain in the strong conduction regime, the same analog comparison was per-

**Fig. 7.** Experimental comparison of  $A_V$  as a function of temperature among Line-TFET, FinFET-TFET and FinFET MOSFET, for FinFET-TFET optimal bias point  $(V_{GS}=1.7\ V\ and\ V_{DS}=0.9\ V)$ .

**Fig. 8.** Experimental comparison of  $A_V$  as a function of temperature among Line-TFET, GAA-TFET (with different source compositions) and GAA-MOSFET, for GAA-TFET optimal bias point ( $V_{GS}$  = 1.7 V and  $V_{DS}$  = 1.5 V).

formed, but now considering Line-TFETs and vertical GAA structures (Si-MOSFETs and TFETs with Si and Si $_{0.73}$ Ge $_{0.27}$  sources) as can be seen in Fig. 8. Since the line-TFETs reaches a higher BTBT current while GAA structures are more TAT dependent, the GAA-TFETs present higher A $_{\rm V}$  values than the Line TFETs, independent on the source composition.

However when the Line-TFET is compared with a GAA MOSFET, the Line TFET seems to be better again.

Although Line-TFETs do not reach  $A_V$  values as high as for GAA-TFETs and Fin-TFETs, when a high on-state current is required, the planar Line-TFET can be considered as an alternative, since it reaches on-state currents much higher than the other TFET structures studied in this paper.

### 4. Conclusion

This paper presents an analysis of the intrinsic voltage gain of Line-TFETs and makes a comparison with devices fabricated with vertical GAA and FinFET structures for both TFET and MOSFET technologies. The results show that this planar line-TFET architecture does not present the highest A<sub>V</sub> values when compared with the two other vertical TFET architectures (FinFET-TFET and GAA-TFET), however it reaches a very high on-state current, which till now was a road block for another TFET structures. Therefore it is possible to conclude that Line-TFETs can be a good alternative to replace MOSFETs since it reaches the highest on-state currents and a better intrinsic voltage gain than the advanced MOSFET architectures (at least 30 dB higher than FinFETs and 10 dB higher when compared with GAA-MOSFETs).

#### Acknowledgments

The authors would like to thank CNPq and FAPESP for the financial support during the execution of this work. Part of the work has been performed within the frame of imec's Core Partner program on Logic Devices.

#### References

- [1] Ionescu AM, Riel H. Tunnel field-effect transistors as energy-efficient electronics switches. Nature 2011;479:329–37.

- [2] Verhulst A et al. Complementary silicon-based heterostructure tunnel-FETs with high tunnel rates. IEEE Electron Dev Lett 2008;29(12):1398–401.

- [3] Nah J et al. Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell nanowire tunneling field-effect transistors. IEEE Trans Electron Dev 2010;57(8):1883–8.

- [4] Verreck D et al. Quantum mechanical performance predictions of p-n-i-n versus pocketed line tunnel field-effect transistors. IEEE Trans Electron Dev 2013;60(7):2128–34.

- [5] Schmidt M et al. Line and point tunneling in scaled Si/SiGe heterostructure TFETs. IEEE Electron Dev Lett 2014;35(7):699–701.

- [6] Walke AM et al. Fabrication and analysis of a Si/Si<sub>0.55</sub>Ge<sub>0.45</sub> heterojunction line tunnel FET. IEEE Trans Electron Dev 2014;61(3):707–15.

- [7] Agopian PGD et al. Experimental comparison between trigate p-TFET and p-FinFET analog performance as a function of temperature. IEEE Trans Electron Dev 2013;60:2493-7.

- [8] Agopian PGD et al. Influence of the source composition on the analog performance parameters of vertical nanowire-TFETs. IEEE Trans Electron Dev 2015;62:16–22.

- [9] Zhao Q-T et al. Strained Si and SiGe nanowire tunnel FETs for logic and analog applications. J Electron Dev Soc 2015;3(3):103–14.

- [10] Sedighi B et al. IEEE Trans Circ Syst-I: Regular Pap 2015;62(1).

- [11] Agopian PGD et al. Comparison between vertical silicon NW-TFET and NW-MOSFET from analog point of view. EuroSOI-ULIS 2015:233.

- [12] Martino JA et al. The impact of the Ge concentration in the source for vertical tunnel-FETs. ECS Trans 2015;66(4):79–86. doi: <a href="http://dx.doi.org/10.1149/06604.0079ecst">http://dx.doi.org/10.1149/ 06604.0079ecst</a>.

- [13] Sivieri VB, Agopian PGD, Martino JA. Impact of diameter on TFET conduction mechanisms. In: 30th Symposium on microelectronics technology and devices (SBMicro). p. 1–4. doi: <a href="http://dx.doi.org/10.1109/SBMicro.2015.7298146">http://dx.doi.org/10.1109/SBMicro.2015.7298146</a>.

- [14] Schulte-Braucks C et al. Experimental demonstration of improved analog device performance in GAA-NW-TFETs. In: 44th European Solid State Device Research Conference (ESSDERC). p. 178–81. 10.1109/ESSDERC.2014.6948789.