# Impact of the NW-TFET Diameter on the Efficiency and the Intrinsic Voltage Gain From a Conduction Regime Perspective

Caio C. M. Bordallo, *Member, IEEE*, Victor B. Sivieri, João Antonio Martino, *Senior Member, IEEE*, Paula G. D. Agopian, *Senior Member, IEEE*, Rita Rooyackers, Anne Vandooren, Eddy Simoen, Aaron Voon-Yew Thean, *Senior Member, IEEE*, and Cor Claeys, *Fellow, IEEE*

Abstract—In this work, the impact of the diameter on vertical nanowire tunnel field effect transistors is analyzed focusing on the conduction mechanism and analog parameters, considering different conduction regimes. The diameter influence is investigated using experimental and simulation data. The impact of the diameter on the analog parameters is analyzed, considering both weak and strong conduction. For a smaller diameter, the impact of band-to-band tunneling (BTBT) on the device characteristics increases, showing opposite trends for weak and strong conduction. For strong conduction, a degradation of the intrinsic voltage gain occurs for very small diameters, because the device has less available area for the occurrence of tunneling. For weak conduction, the reduction of the diameter increases the BTBT along the channel/source junction without showing this degradation.

**Index Terms**—Analog performance, band-to-band tunneling (BTBT), conduction mechanism, tunnel field effect transistor (TFET).

# I. INTRODUCTION

TUNNEL field effect transistors (TFETs) are devices in which the designed conduction mechanism is the band-to-band tunneling (BTBT) [1]. TFETs are candidate solutions for low-power/low-voltage applications due to their capability to overcome, at room temperature, the theoretical silicon (Si) MOSFET limit of 60 mV/dec for the subthreshold swing [2]–[4].

Manuscript received February 24, 2016; revised April 18, 2016; accepted April 22, 2016. Date of publication May 10, 2016; date of current version June 17, 2016. This work was supported in part by the Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) and the State of São Paulo Research Foundation (FAPESP), in part by the CNPq–Research Foundation-Flanders, and in part by the imec's Logic Device Program and its core partners. The review of this paper was arranged by Editor A. Haque.

- C. C. M. Bordallo, V. B. Sivieri, and J. A. Martino are with the University of São Paulo, São Paulo 05508-010, Brazil (e-mail: caiobordallo@gmail.com; victor.sivieri@gmail.com; martino@lsi.usp.br).

- P. G. D. Agopian is with the University of Sao Paulo, São Paulo 05508-010, Brazil, and also with São Paulo State University, São João da Boa Vista 01049-010, Brazil (e-mail: agopian@lsi.usp.br).

- R. Rooyackers, A. Vandooren, E. Simoen, and A. Voon-Yew Thean are with imec, Leuven 3010, Belgium (e-mail: rooyack@imec.be; vdoorena@imec.be; simoen@imec.be; aaron.thean@imec.be).

- C. Claeys is with imec, Leuven 3010, Belgium, and also with the Electrical Engineering Department, Katholieke Universiteit Leuven, Leuven 3001, Belgium (e-mail: claeys@imec.be).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2016.2559580

Although the BTBT mechanism allows an increase in the switching speed of the transistor, it provides a very low ON-state current ( $I_{\rm ON}$ ) in conventional Si TFETs. One strategy that is widely used to improve this parameter is the use of different materials with a reduced bandgap at the source of the devices. The reduced bandgap of the source leads to a reduction of the tunneling path, which improves the BTBT mechanism, increasing the  $I_{\rm ON}$  [5]–[8].

Even though the TFET device was developed in order to replace the conventional MOSFET for switching applications, recent studies have been done focusing on their analog behavior, demonstrating that TFETs also have a good potential for analog applications [9]–[13]. The TFETs show promising analog performance since BTBT is their dominant conduction mechanism, which presents low output conduction values (high early voltage) when compared with MOSFET devices [14], provided the channel length is sufficiently large to avoid drain induced barrier thinning [15].

Heading in the same direction as the MOSFETs, new device architectures have been studied to increase the electrostatic control by the gate. One promising technology is the vertical nanowire, which is a gate all around structure [16]. The use of this structure in TFET devices improves the control of the tunneling carriers, improving  $I_{\rm ON}$ , the transconductance, the subthreshold swing, and other important analog parameters [17], [18].

In this work, the effect of the diameter in vertical nanowire TFETs is investigated focusing on the conduction mechanism and its influence on the analog parameters, thereby considering different conduction regimes. The analyzed analog parameters were the transistor efficiency (gm/ $I_{DS}$ ), the transconductance (gm), the output conduction ( $g_D$ ), and the intrinsic voltage gain ( $A_V$ ).

# II. EXPERIMENTAL AND SIMULATION DETAILS

The experimental data have been obtained on vertical nanowire TFETs fabricated at imec, in Belgium. The devices are n-type NW-TFETs that use a top down vertical process flow [19], with a total channel length ( $L_{\rm CH}$ ) of 220 nm, a physical gate length ( $L_G$ ) of 150 nm, a gate/source overlap ( $L_{\rm GS}$ ) of 30 nm and a gate/drain underlap ( $L_{\rm GD}$ ) of 100 nm.

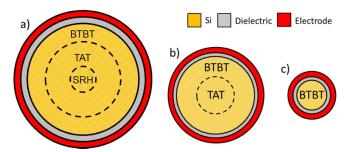

Fig. 1. Structure of the studied devices.

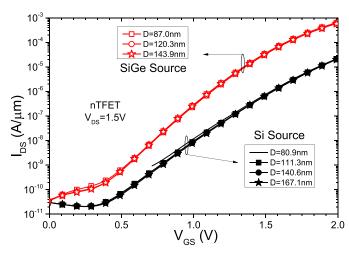

Fig. 2. Experimental normalized drain current as a function of gate bias for TFETs with different diameters and two source compositions.

The schematic of the experimental device is presented in Fig. 1. The gate dielectric consists of 3 nm of  $HfO_2$  on top of 1 nm of  $SiO_2$ , resulting in an equivalent oxide thickness of 2 nm. The drain region is doped with  $2 \times 10^{19}$  at/cm<sup>3</sup> As, the channel is lightly doped with  $1 \times 10^{16}$  at/cm<sup>3</sup> As, and the source is doped with  $1 \times 10^{20}$  at/cm<sup>3</sup> boron. Two different source compositions were studied, one of pure Si and the other of  $Si_{0.73}Ge_{0.27}$ . The  $Si_{0.73}Ge_{0.27}$  source is obtained by the deposition of a layer of  $Si_{0.73}Ge_{0.27}$  on top of the lightly doped silicon channel layer. More details regarding these structures can be found in [7].

The experimental devices used in this work have an effective diameter ranging from 167 down to 81 nm and have 2400 nanowires in parallel.

Simulations of the TFET performance were performed for nanowire diameters beyond the experimental values using the Atlas simulator from Silvaco without including quantum confinement models, considering the different current conduction mechanisms: Shockley–Read–Hall (SRH) recombination, trap assisted tunneling (TAT), and nonlocal BTBT. The simulation was used to reach diameters down to 15 nm.

# III. ANALYSIS AND RESULTS

Fig. 2 shows the drain current  $(I_{DS})$ , normalized by the diameter, as a function of the gate voltage  $(V_{GS})$  for two

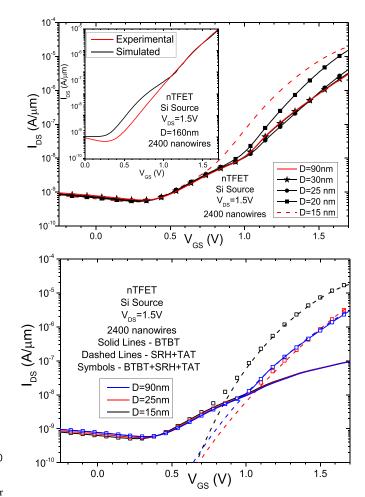

Fig. 3. Simulated normalized drain current as a function of gate bias for TFETs with (a) different diameters and the calibration in the inset and (b) its current composition.

different devices, one with a source of pure Si and another with a composition of  $Si_{0.73}Ge_{0.27}$ . Initially, one can observe that the on-state  $I_{DS}$  for the SiGe source device is higher than for the Si source counterpart due to the reduction of the tunnel path caused by the lower bandgap energy of the SiGe source [7].

One important characteristic that can be noted is that the normalized  $I_{DS}$  remains almost independent on the diameter, for all the available diameters, considering devices with both source compositions. For wide diameters, there is only a diameter influence on the nonnormalized  $I_{DS}$  [20].

In order to extrapolate the results for smaller diameters, numerical simulations have been carried out for diameters down to 15 nm. Fig. 3(a) shows the  $I_{\rm DS}$ , normalized by the diameter, as a function of  $V_{\rm GS}$  for simulated Si source nTFETs with smaller diameters. The inset of Fig. 3 illustrates the calibration used for the simulation. From Fig. 3, it is possible to observe that there is a noticeable increase in the normalized  $I_{\rm ON}$  with the reduction of the diameter. This increase in the ON-state current is related with the dominant conduction mechanism. These results suggest that for narrower NW-TFETs, the gate to channel coupling is better, resulting in a higher BTBT current.

Fig. 4. Schematic of the cross section of a vertical nanowire nTFET with (a) large, (b) medium, and (c) small diameters, highlighting their dominant conduction mechanism as demonstrated by simulated data in Fig. 8.

TFETs can present three types of current mechanisms: 1) generation and recombination (SRH); 2) TAT; and 3) BTBT. The discretized conduction mechanism components are presented in Fig. 3(b), for different diameters. Fig. 4 shows a representation of a cross section of the source/channel junction of the used nanowire nTFET. In larger diameter devices [Fig. 4(a)], the current conduction is dominated by BTBT only near the Si/Oxide interface. As the potential decreases toward the center of the nanowire, the conduction band of the channel region becomes more distant from the valence band of the source. This generates a transition among the predominant conduction mechanisms along the diameter, with BTBT the predominant mechanism near the surface, becoming TAT at intermediate positions and closer to the center mainly SRH occurs.

For a medium size diameter [Fig. 4(b)], there is sufficient interaction of the gate potential in the center of the device, leading to an increase of the BTBT and TAT influence on the center. This results in a predominance of BTBT near the surface and a predominance of TAT in the center. For a small diameter [Fig. 4(c)], the impact of the gate potential at the center of the device is strong enough to guarantee that BTBT is the dominant mechanism along all the diameter of the nanowire [20].

The fact that the BTBT has become the dominant mechanism along the whole cross section is responsible for the increase in the normalized  $I_{\rm DS}$  considering smaller diameters in Fig. 3(a). From Fig. 3(a), it is also possible to observe that the onset voltage ( $V_{\rm ON}$ ), the minimum gate voltage necessary for BTBT to become the dominant mechanism, decreases for a narrower nanowire, in agreement with the observations in [21].

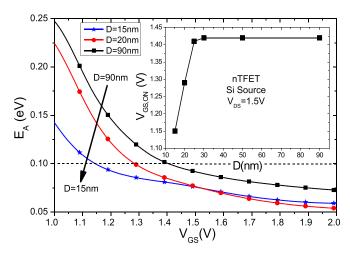

In order to investigate this phenomenon,  $V_{\rm ON}$  has been extracted (inset of Fig. 5) using the activation energy ( $E_A$ ) criterion [7]. This criterion defines that for an  $E_A$  higher than 0.5 eV, the dominant conduction mechanism is SRH, for an  $E_A$  lower than 0.1 eV, the dominant mechanism is BTBT, and for  $E_A$  values between 0.5 and 0.1 eV, the dominant mechanism is TAT.

Fig. 5 presents the  $E_A$  as a function of  $V_{\rm GS}$  for different diameters, obtained by the Arrhenius method, which is extracted using (1). From Fig. 5, it is possible to obtain the  $V_{\rm ON}$  by analyzing the  $V_{\rm GS}$  value when  $E_A$  is 0.1 eV (inset of Fig. 5). One can notice that for the larger diameters, the  $V_{\rm ON}$  is almost constant, but when the diameter is reduced to values lower than 30 nm,  $V_{\rm ON}$  starts to decrease, reducing

Fig. 5. Activation energy as a function of gate bias for a simulated nTFET with different diameters. Inset: onset voltage as a function of the diameter.

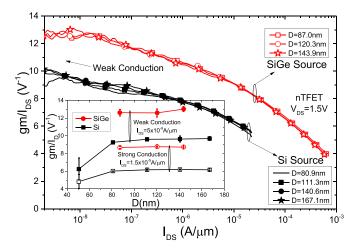

Fig. 6. Experimental efficiency as a function of the normalized drain current for TFETs with different diameters and two source compositions.

almost 300 mV when comparing the largest and the smallest diameter

$$\ln(I_{\rm DS}) = -\left(\frac{E_A}{K \cdot T}\right) + \ln(I_0) \tag{1}$$

where K is the Boltzmann constant, T the temperature in kelvin, and  $I_0$  is the OFF-state drain current.

These small-diameter effects can also be observed when analyzing the analog parameters of the devices. One very important parameter for the analog performance is the transistor efficiency (gm/ $I_{DS}$ ). The analysis of the efficiency on the experimental devices for both source materials (Fig. 6) pointed out that as the available measured diameters are considerably large, the diameter has almost no influence on the measured efficiency characteristics, for both weak and strong conduction conditions.

Although the diameter has almost no influence on the efficiency, the efficiency for the SiGe source device is higher than for the Si source counterpart, for any conduction regime, due to the lower bandgap energy of the SiGe source, increasing all the conduction mechanisms.

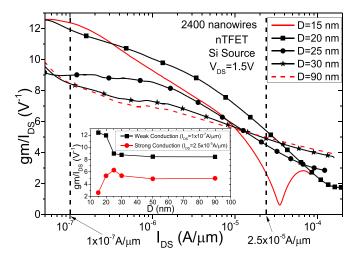

Fig. 7. Simulated efficiency as a function of drain current for Si source TFETs with different diameters.

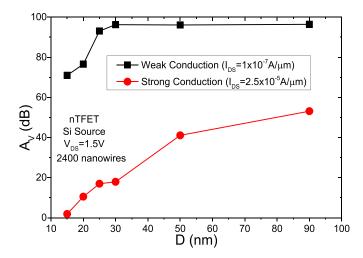

When using numerical simulations to extrapolate the impact of the reduction of the diameter on the analog characteristics of Si-source vertical nanowire nTFETs, some interesting results can be observed. Comparing the efficiency (Fig. 7), two opposite trends can be observed: one for the weak conduction  $(I_{\rm DS}=1\times10^{-7}{\rm A}/\mu{\rm m})$  and another for the strong conduction  $(I_{\rm DS}=2.5\times10^{-5}~{\rm A}/\mu{\rm m})$ .

In weak conduction, i.e., the condition for which the efficiency reflects the subthreshold swing behavior, the efficiency is higher for small diameter devices. This behavior can be explained by the higher influence of the BTBT on the devices with small diameter, because the current generated by the BTBT leads to a better switching characteristic, which reduces the subthreshold swing, resulting in an improvement of the efficiency.

However, in strong conduction, which has higher values of  $I_{\rm DS}$ , the narrower devices have insufficient area to provide an increase of the BTBT mechanism, resulting in a decrease of the efficiency when compared to larger devices that do not have BTBT as the dominant mechanism toward the center of the nanowire.

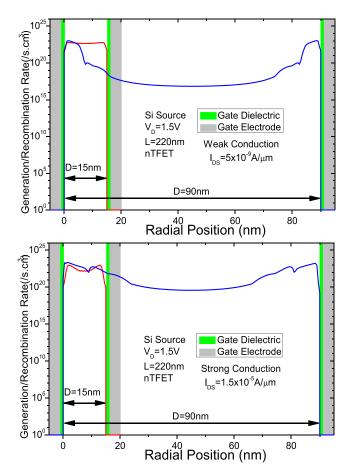

In order to better understand the diameter effect on the conduction mechanism for different conduction regions, Fig. 8 presents the generation rate as a function of the radial position of the nanowire toward the center.

From Fig. 8, it is possible to observe that for the weak conduction [Fig. 8(a)], the smaller diameter device has BTBT all along the channel/source junction, while the device with a larger diameter has BTBT only near the Si/dielectric interfaces. However, for strong conduction [Fig. 8(b)], the larger diameter device has a more pronounced BTBT in the center of the device, improving the resulting BTBT for this conduction condition.

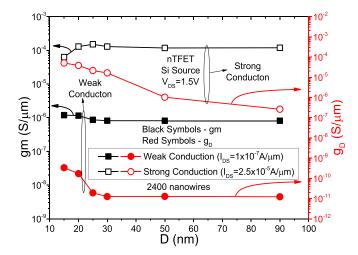

The results presented in Fig. 8 can also explain the behavior of other analog parameters, as the transconductance (gm) and the output conductance ( $g_D$ ) (Fig. 9), both normalized by the diameter. Differently as done in [9], [10], and [12]–[14], in this paper, the same  $I_{\rm DS}$  level is used to compare these parameters.

Fig. 8. Simulated generation rate as a function of radial position for Si source NW-TFETs in (a) weak and (b) strong conduction.

Fig. 9. Simulated normalized transconductance and output conductance as a function of the diameter for both weak and strong conduction.

From Fig. 9, analyzing initially the transconductance, it can be noticed that for the weak conduction regime, as the diameter is strongly reduced, the gm is increased due to the increase of the gate to channel electrostatic coupling and consequently of the BTBT predominance in the current. For strong conduction, the diameter reduction also improves the gm, but only until the device is narrow enough to ensure that

Fig. 10. Simulated intrinsic voltage gain as function of the diameter.

the BTBT dominates along the entire junction. For diameters lower than this point, gm tends to be degraded due to the limitation of the BTBT area.

The BTBT mechanism is more susceptible to the drain bias than TAT due to the BTBT dependence on the total electric field ( $\xi$ ). This dependence can be studied by the model of the generation rate of the BTBT mechanism (RBTBT) proposed in [22] as shown in

$$R_{\text{BTBT}} = A \cdot \frac{n \cdot p - n_i^2}{(n + n_i)(p + n_i)} \cdot \xi^P \cdot e^{\left(\frac{B \cdot E_g \cdot (7)^{3/2}}{E_g \cdot (300)^{3/2} \cdot \xi}\right)} \tag{2}$$

where n is the electron concentration, p is the hole concentration,  $n_i$  is the intrinsic carrier concentration, T is the temperature,  $E_g$  is the bandgap, P is the electric field concentration parameter, A is the pre-exponential constant of the model, and B is the exponential constant of the model.

Since the output conductance is strongly influenced by the drain bias, the same analysis of gm is done for  $g_D$ . The output conductance has the same behavior for both conduction conditions: the  $g_D$  tends to increase (degrade) as the diameter becomes smaller due to the higher influence of the BTBT. Due to the higher influence of BTBT under strong conduction, it starts to degrade for larger diameters, increasing almost 2 orders of magnitude compared with the smallest simulated device.

When considering the influence of the diameter for both conduction conditions on the intrinsic voltage gain  $(A_V)$ , which is given in (3), an interesting behavior can be noticed (Fig. 10). Under strong conduction, as the  $g_D$  is increased more pronounced for a smaller nanowire diameter than the increase of the gm,  $A_V$  has very low values and is strongly degraded with reduced diameter

$$A_V = 20 \cdot \log \left( \left| \frac{gm}{g_D} \right| \right). \tag{3}$$

Analyzing the device under weak conduction for large diameters, lowering the diameter has almost no influence on  $A_V$ . However, for the smaller diameters, the degradation of the  $g_D$  is more pronounced than the increase of the gm, resulting in

a degradation of  $A_V$ . At the same time, this degradation for the nanowire TFET in weak conduction is much lower than the one in strong conduction.

### IV. CONCLUSION

In this work, the performance of vertical nanowire TFETs is investigated in function of the diameter with a focus on the conduction mechanism and the analog parameters, considering different conduction conditions.

For large diameters, the devices are hardly influenced by the reduction of the diameter. As the diameter becomes smaller, BTBT starts to become the dominant mechanism along the channel/source junction. Furthermore, the onset voltage starts to decrease as well. These two effects together generate an increase in the normalized drain current.

For narrower nanowire TFETs at strong conduction, the current generated by BTBT degrades due to the lower available area for tunneling occurrence. However, for weak conduction, the reduction of the diameter increases the BTBT along the channel/source junction without this degradation.

Concerning the analog parameters, for both conduction conditions, the transconductance is improved for narrow nanowires. However, the output conductance is more degraded, resulting in a degradation of the output conductance with the reduction of the diameter. Furthermore, the degradation at strong conduction is more pronounced than at weak conduction.

## REFERENCES

- W. M. Reddick and G. A. J. Amaratunga, "Silicon surface tunnel transistor," *Appl. Phys. Lett.*, vol. 67, no. 4, pp. 494–496, Jul. 1995.

- [2] M. Kim, Y. Wakabayashi, R. Nakane, M. Yokoyama, M. Takenaka, and S. Takagi, "High I<sub>on</sub>/I<sub>off</sub> Ge-source ultrathin body strained-SOI tunnel FETs," in *IEDM Tech. Dig.*, Dec. 2014, pp. 13.2.1–13.2.4.

- [3] T. Krishnamohan, D. Kim, S. Raghunathan, and K. Saraswat, "Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and «60 mV/dec subthreshold slope," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–3.

- [4] W. Y. Choi, B.-G. Park, J. D. Lee, and T.-J. K. Liu, "Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 743–745, Aug. 2007.

- [5] A. S. Verhulst, W. G. Vandenberghe, K. Maex, and G. Groeseneken, "Boosting the on-current of a n-channel nanowire tunnel field-effect transistor by source material optimization," *J. Appl. Phys.*, vol. 104, no. 6, p. 064514, Sep. 2008.

- [6] D. Leonelli, A. Vandooren, R. Rooyackers, S. De Gendt, M. M. Heyns, and G. Groeseneken, "Drive current enhancement in p-tunnel FETs by optimization of the process conditions," *Solid-State Electron.*, vols. 65–66, pp. 28–32, Dec. 2011.

- [7] A. Vandooren et al., "Analysis of trap-assisted tunneling in vertical Si homo-junction and SiGe hetero-junction tunnel-FETs," Solid-State Electron., vol. 83, pp. 50–55, May 2013.

- [8] M. Schmidt et al., "Line and point tunneling in scaled Si/SiGe heterostructure TFETs," IEEE Electron Device Lett., vol. 35, no. 7, pp. 699–701, Jul. 2014.

- [9] P. G. D. Agopian et al., "Influence of the source composition on the analog performance parameters of vertical nanowire-TFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 1, pp. 16–22, Jan. 2015.

- [10] M. D. V. Martino et al., "Analog performance of vertical nanowire TFETs as a function of temperature and transport mechanism," Solid-State Electron., vol. 112, pp. 51–55, Oct. 2015.

- [11] A. Mallik and A. Chattopadhyay, "Tunnel field-effect transistors for analog/mixed-signal system-on-chip applications," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 888–894, Apr. 2012.

- [12] P. G. D. Agopian et al., "NW-TFET analog performance for different Ge source compositions," in Proc. IEEE SOI-3D-Subthreshold Microelectron. Technol. Unified Conf. (S3S), Oct. 2013, pp. 1–4.

- [13] P. G. D. Agopian, J. A. Martino, R. Rooyackers, A. Vandooren, E. Simoen, and C. Claeys, "Experimental comparison between trigate p-TFET and p-FinFET analog performance as a function of temperature," *IEEE Trans. Electron Devices*, vol. 60, no. 8, pp. 2493–2497, Aug. 2013.

- [14] P. G. D. Agopian *et al.*, "Comparison between vertical silicon NW-TFET and NW-MOSFET from analog point of view," in *Proc. EUROSOI-ULIS*, Jan. 2015, pp. 233–236.

- [15] R. Vishnoi and M. J. Kumar, "Compact analytical model of dual material gate tunneling field-effect transistor using interband tunneling and channel transport," *IEEE Trans. Electron Devices*, vol. 61, no. 6, pp. 1936–1942, Jun. 2014.

- [16] J.-P. Colinge, "From gate-all-around to nanowire MOSFETs," in *Proc. Int. Semiconductor Conf.*, Oct./Sep. 2007, pp. 11–17.

- [17] R. Vishnoi and M. Kumar, "Compact analytical drain current model of gate-all-around nanowire tunneling FET," *IEEE Trans. Electron Devices*, vol. 61, no. 7, pp. 2599–2603, Jul. 2014.

- [18] C. Schulte-Braucks, S. Richter, L. Knoll, L. Selmi, Q.-T. Zhao, and S. Mantl, "Experimental demonstration of improved analog device performance in GAA-NW-TFETs," in *Proc. 44th Eur. Solid State Device Res. Conf. (ESSDERC)*, Sep. 2014, pp. 178–181.

- [19] R. Rooyackers et al., "A new complementary hetero-junction vertical tunnel-FET integration scheme," in *IEDM Tech. Dig.*, Dec. 2013, pp. 4.2.1–4.2.4.

- [20] C. C. M. Bordallo *et al.*, "Impact of the diameter of vertical nanowire-tunnel FETs with Si and SiGe source composition on analog parameters," in *Proc. EUROSOI-ULIS*, Jan. 2015, pp. 253–256.

- [21] E.-H. Toh, G. H. Wang, G. Samudra, and Y.-C. Yeo, "Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization," *Appl. Phys. Lett.*, vol. 90, p. 263507, Jun. 2007.

- [22] G. A. M. Hurkx, D. B. M. Klaassen, and M. P. G. Knuvers, "A new recombination model for device simulation including tunneling," *IEEE Trans. Electron Devices*, vol. 39, no. 2, pp. 331–338, Feb. 1992.

Caio C. M. Bordallo (M'14) received the B. Eng. degree in electrical engineering and the M.Sc. degree from the Centro Universitário da FEI, São Bernardo do Campo, Brazil. He is currently pursuing the Ph.D. degree in microelectronics with the University of São Paulo (USP), São Paulo, Brazil.

He has been with the CMOS-SOI Research Group, USP, since 2014.

**Victor B. Sivieri** received the B. Eng. degree in electrical engineering from the University of São Paulo (USP), São Paulo, Brazil, and the University of Darmstadt, Darmstadt, Germany, where he is currently pursuing the master's degree in microelectronics

He has been with the CMOS-SOI Research Group, USP, since 2014.

**João Antonio Martino** (M'06–SM'07) received the M.S. and Ph.D. degrees in microelectronics from the University of São Paulo (USP), São Paulo, Brazil.

He holds a post-doctoral position at imec, leuven, Belgium. He has been a Professor with USP since 2005 and the Head of the SOI Research Group since 1990.

**Paula G. D. Agopian** (M'09–SM'15) received the M.S. and Ph.D. degrees in microelectronics from the University of São Paulo (USP), São Paulo, Brazil.

She is currently with São Paulo State University (UNESP), São João da Boa Vista and LSI/USP, where she is involved in the field of tunnel FET devices.

**Rita Rooyackers** received the B.S. degree in industrial chemistry from the Rega Institute, Katholieke Universiteit Leuven, Leuven, Belgium.

She is currently with imec, Leuven, where she is involved in the field of tunnel FET technology development.

**Anne Vandooren** received the Ph.D. degree in electrical engineering from the University of California at Davis, Davis, CA, USA, in 2000.

She is currently a Senior Researcher with imec, Leuven, Belgium, where she is involved in nanowire devices and tunneling-based transistors.

**Eddy Simoen** received the M.S. and Ph.D. degrees in engineering from Ghent University, Ghent, Belgium, in 1980 and 1985, respectively.

He has been with imec, Leuven, Belgium, since 1986, where he is currently a Scientist.

**Aaron Voon-Yew Thean** (SM'15) received the B.Sc., M.Sc., and Ph.D. degrees from the University of Illinois at Champaign–Urbana, Urbana, IL, USA, all in electrical engineering.

He is currently the Director of the Logic Program with imec, Leuven, Belgium.

Cor Claeys (M'94–SM'95–F'09) received the Ph.D. degree from the Katholieke Universiteit Leuven (KU Leuven), Leuven, Belgium.

He has been a Professor with KU Leuven since 1990. Since 1984, he has been with imec, Leuven.